Solved Given The Risc V Processor Implementation Below Chegg

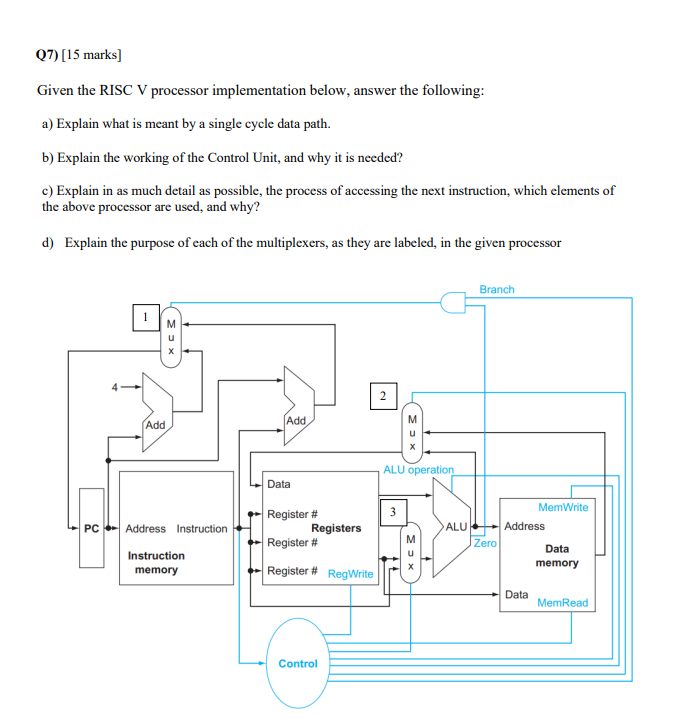

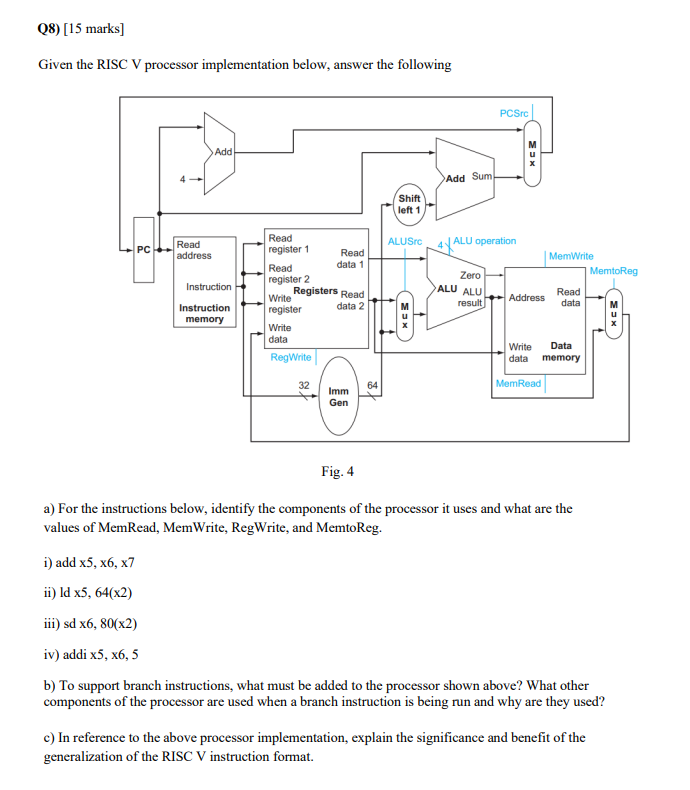

Solved Given The Risc V Processor Implementation Below Chegg Question: given the risc v processor implementation below, answer the following fig,4 a) for the instructions below, identify the components of the processor it uses and what are the values of memread, memwrite, regwrite, and memtoreg. 5 stage pipeline implementation of risc v 32i processor. in this repository i have implemented 5 stage pipelined processor which is actually the conversion of my previous single cycle implementation of processor into pipeline. link to previous single cycle implementation is given as: github.

Solved Given The Risc V Processor Implementation Below Chegg 1. consider a version of the pipeline from section 4.5 in risc v text that does not handle data. This project is a system verilog implementation of a 5 stage pipelined risc v processor. the pipelining technique is a fundamental concept in modern processor design, enabling improved instruction throughput and performance by overlapping instruction execution stages. When testing your emulator, test the following by assembling using the given linker script org.lds. determine the length of a c style string by adding 1 until we find the terminator ‘\0’. copy one c style string into another. i expanded the actual implementation to make it easier to see each element in assembly. into the destination. In this lecture, the instruction set architecture (isa) of the risc v processor will be introduced. we will only consider the base instruction set for the 32 bit integer version of the isa.

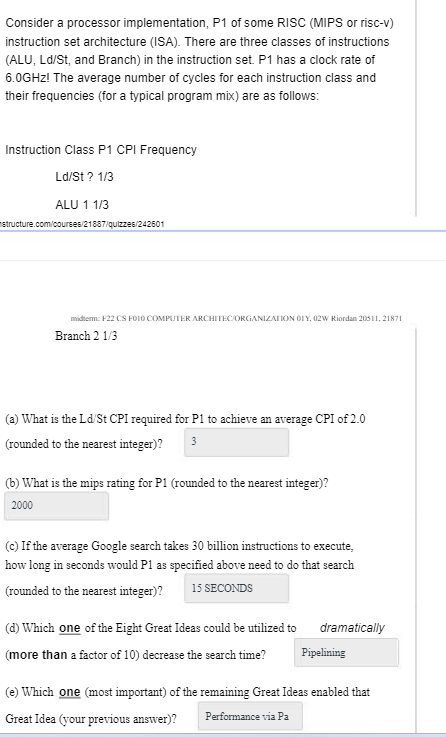

Solved Consider A Processor Implementation P1 Of Some Risc Chegg When testing your emulator, test the following by assembling using the given linker script org.lds. determine the length of a c style string by adding 1 until we find the terminator ‘\0’. copy one c style string into another. i expanded the actual implementation to make it easier to see each element in assembly. into the destination. In this lecture, the instruction set architecture (isa) of the risc v processor will be introduced. we will only consider the base instruction set for the 32 bit integer version of the isa. Risc v’s pipeline performance due to realistic assumptions of hazard situations. a benchmark consists of 27% loads, 1 stores, 45% alu operations, 15% conditional branches, 3 % unconditional branches. Our expert help has broken down your problem into an easy to learn solution you can count on. question: given the risc v processor implementation below, answer the following: a) explain what is meant by a single cycle data path. b) explain the working of the control unit, and why it is needed?. You will develop riscv assembly language implementations of the following problems, and print the results to ensure that both the c implementation and your riscv implementation compute the correct answer. In implementing the processor, you can use components from the “prim” library of the quartus ii software. you can also use the “megawizard” to help you design the memory unit as well as other functional units.

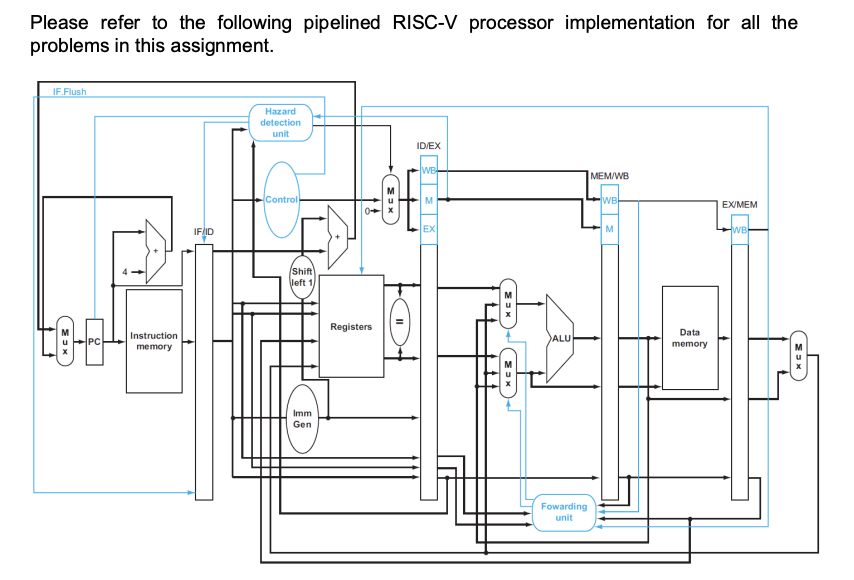

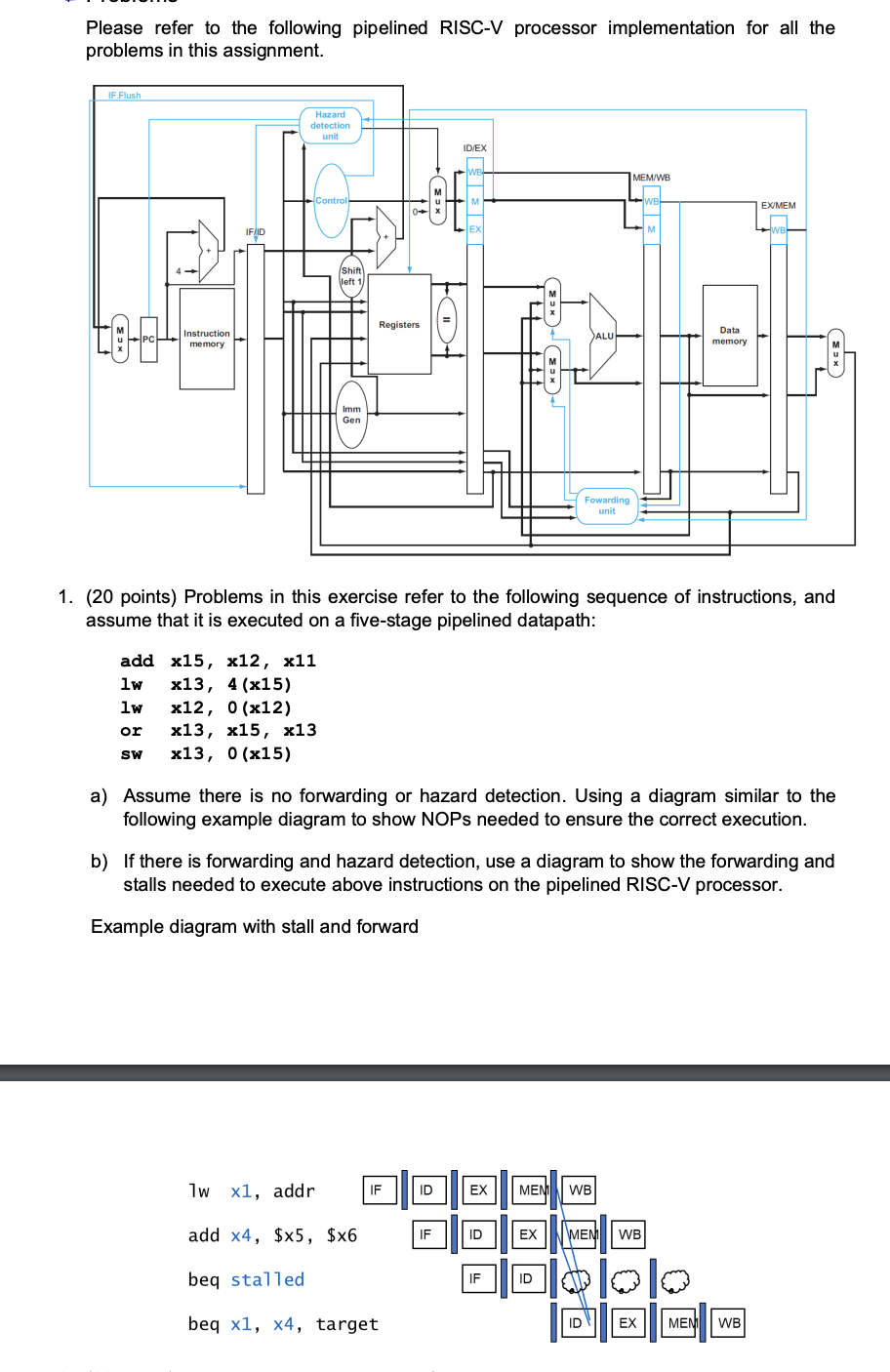

Solved Please Refer To The Following Pipelined Risc V Chegg Risc v’s pipeline performance due to realistic assumptions of hazard situations. a benchmark consists of 27% loads, 1 stores, 45% alu operations, 15% conditional branches, 3 % unconditional branches. Our expert help has broken down your problem into an easy to learn solution you can count on. question: given the risc v processor implementation below, answer the following: a) explain what is meant by a single cycle data path. b) explain the working of the control unit, and why it is needed?. You will develop riscv assembly language implementations of the following problems, and print the results to ensure that both the c implementation and your riscv implementation compute the correct answer. In implementing the processor, you can use components from the “prim” library of the quartus ii software. you can also use the “megawizard” to help you design the memory unit as well as other functional units.

Solved Please Refer To The Following Pipelined Risc V Chegg You will develop riscv assembly language implementations of the following problems, and print the results to ensure that both the c implementation and your riscv implementation compute the correct answer. In implementing the processor, you can use components from the “prim” library of the quartus ii software. you can also use the “megawizard” to help you design the memory unit as well as other functional units.

Comments are closed.