Solved 3 Consider The Module Below Module Examplela Chegg

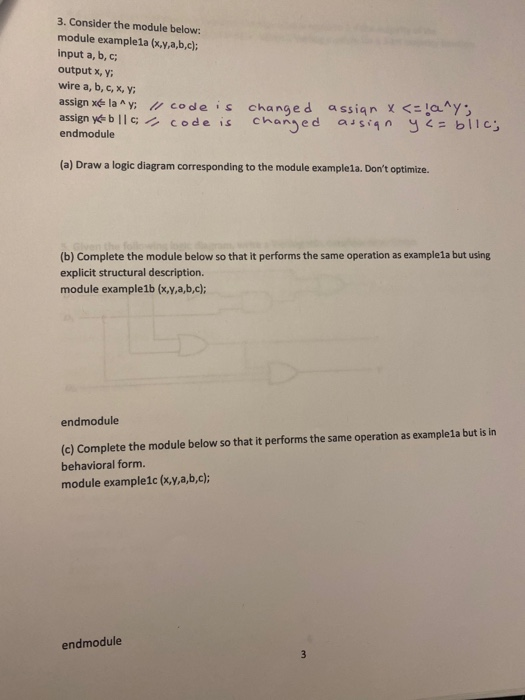

Solved 3 Consider The Module Below Module Examplela Chegg Don't optimize. (b) complete the module below so that it performs the same show transcribed image text here’s the best way to solve it. The given systemverilog module takes a 4 bit input 'aa' and produces a single bit output 'bb'. the operation performed is a bitwise xor (^) of 15 repetitions of the 3 most significant bits of 'aa'.

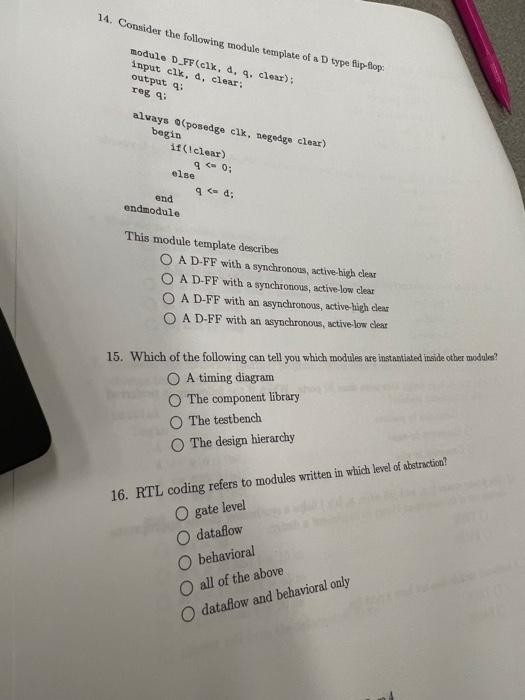

Solved 14 Consider The Following Module Template Of A D Chegg Each module performs a specific function and can be connected with other modules to create more complex systems. this article explains the syntax, purpose, and uses of verilog modules, and also covers the concept of top level modules, testbenches, and hierarchical naming. Consider the module below: module example 3a (x,y,a,b,c); input a, b, c; output x, y; wire a, b, c, x,y; assign x = !a ^y; assign y = b || c; endmodule (a) draw a logic diagram corresponding to the module example3a. don't optimize. (b) rewrite the above module using explicit structural description. (c) rewrite the above module using always. Our expert help has broken down your problem into an easy to learn solution you can count on. here’s the best way to solve it. Assuming the module functions as intended, which of the following hexadecimal test vectors will validate it, in which the bits are interpreted as {aa, bb, bb, bb, bb}?.

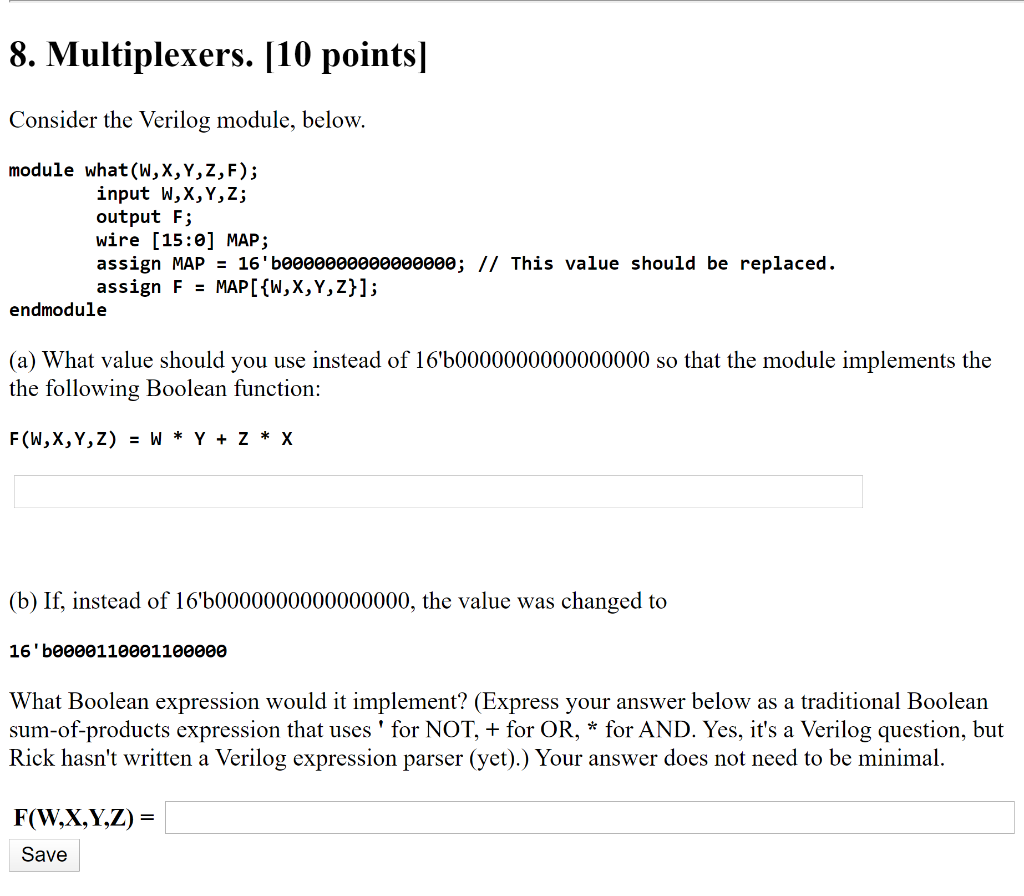

Solved Can I Get Some Help On This Problem Answers And Chegg Our expert help has broken down your problem into an easy to learn solution you can count on. here’s the best way to solve it. Assuming the module functions as intended, which of the following hexadecimal test vectors will validate it, in which the bits are interpreted as {aa, bb, bb, bb, bb}?. There are 2 steps to solve this one. identify that the always comb block for updating the next state is missing a default assignment. in below. Ask any question and get an answer from our subject experts in as little as 2 hours. Question: probleme 3: consider the modul down below to the left. let ita definition in verilog have the first line module m (a, b, c): where a, b are inputs and c is the output. Problem 8: below shows the step response of a 1st order system (i.e., original dynamic system) and the step response of a unit feedback control of this 1st order system with a pi controller (i.e., feedback control system).

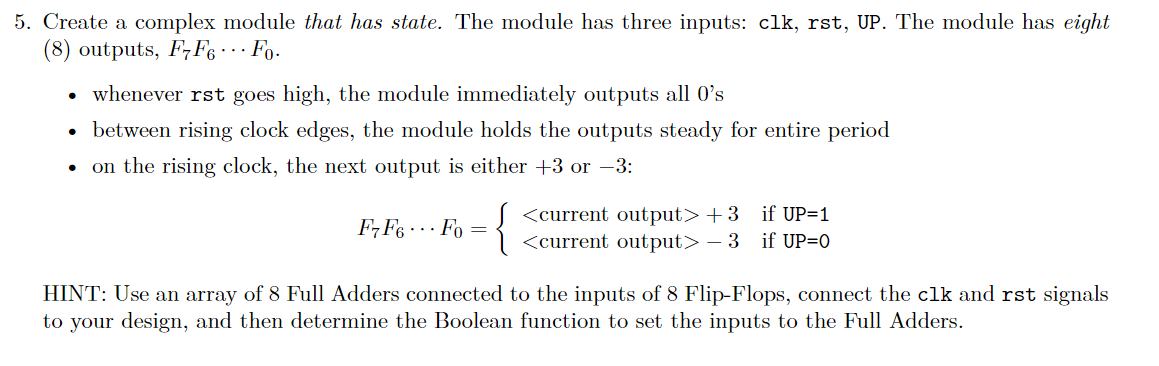

Solved Create A Complex Module That Has State The Module Chegg There are 2 steps to solve this one. identify that the always comb block for updating the next state is missing a default assignment. in below. Ask any question and get an answer from our subject experts in as little as 2 hours. Question: probleme 3: consider the modul down below to the left. let ita definition in verilog have the first line module m (a, b, c): where a, b are inputs and c is the output. Problem 8: below shows the step response of a 1st order system (i.e., original dynamic system) and the step response of a unit feedback control of this 1st order system with a pi controller (i.e., feedback control system).

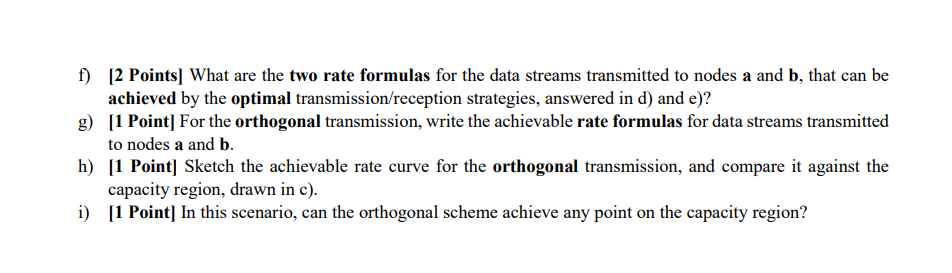

Solved Module 3 Homework 20 Points Consider The 3 Node Chegg Question: probleme 3: consider the modul down below to the left. let ita definition in verilog have the first line module m (a, b, c): where a, b are inputs and c is the output. Problem 8: below shows the step response of a 1st order system (i.e., original dynamic system) and the step response of a unit feedback control of this 1st order system with a pi controller (i.e., feedback control system).

Comments are closed.