Rtl Code Testbench For Multiplexer Verilog Hdl Tutorial

Multiplexer Design Using Verilog Hdl Geeksforgeeks Welcome to this detailed tutorial on designing a multiplexer (mux) using rtl (register transfer level) verilog and building a fully functional testbench for verification!. In this article, we are discussing multiplexer design. below mentioned is the article in which we are going to discuss the problem. design of a 2:1 mux using verilog hardware description language along with testbench.

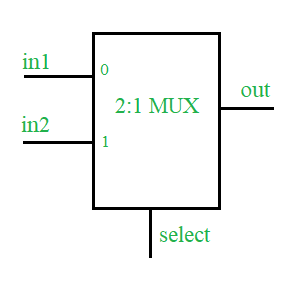

Multiplexer Design Using Verilog Hdl Geeksforgeeks To design and simulate a 4:1 multiplexer (mux) using verilog hdl in four different modeling styles—gate level, data flow, behavioral, and structural and to verify its functionality through a testbench using the vivado 2023.1 simulation environment. In this post, you will learn how to: write the verilog code for a 4:1 mux across all layers of abstraction (modeling styles). generate the rtl schematic for the 4:1 mux and simulate the design using modern testbenches, leveraging the latest simulation tools like vivado and modelsim. This article explores the design and implementation of a 4×1 multiplexer using verilog, a hardware description language (hdl) widely used for modeling and verifying digital systems. In this tutorial, we'll learn all of them. let's start with basic 2x1 mux in gate level modeling. it has two inputs, one select line and one output. the boolean expression for 2x1 is given as y = s i 0 s i 2 for this, we require two and gate, one or gate and one not gate.

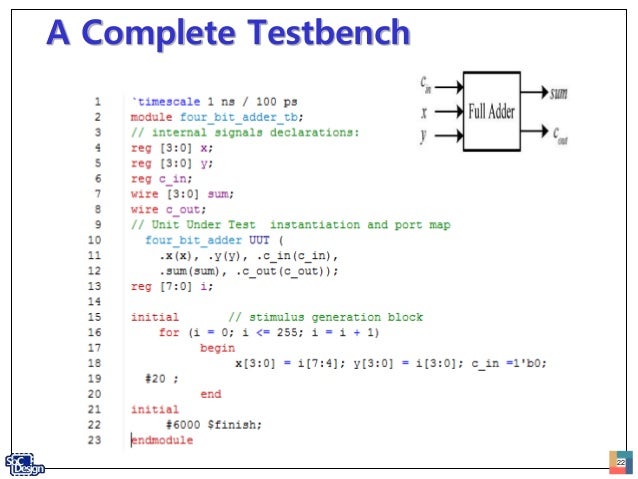

Verilog Hdl This article explores the design and implementation of a 4×1 multiplexer using verilog, a hardware description language (hdl) widely used for modeling and verifying digital systems. In this tutorial, we'll learn all of them. let's start with basic 2x1 mux in gate level modeling. it has two inputs, one select line and one output. the boolean expression for 2x1 is given as y = s i 0 s i 2 for this, we require two and gate, one or gate and one not gate. It explains the functionality of a multiplexer, presents the verilog code for each modeling style, and includes rtl schematics and simulation waveforms. additionally, it addresses common errors in truth tables and offers tips for verifying equations derived from them. This document focuses on using verilog hdl to test digital systems, by giving the designer a handful of simulation techniques that can be used on the majority of digital applications. These verilog code examples and testbenches demonstrate the functionality of 2 to 1 and 4 to 1 multiplexers, along with various test cases to verify their operation. you can use a verilog simulator to run these testbenches and observe the results. Learn the key differences between simulation and synthesis code in verilog, including supported constructs, coding styles, and best practices for hardware design verification.

Comments are closed.