Riscv Piplined Processor Verilog Code Explanation

Github Taepoong719 Riscv Cpu Verilog Risc V Cpu Implemented By Verilog Hi, hope this video will clarify the code a bit. link to github: github ilanmer2205 riscv more. This project is a system verilog implementation of a 5 stage pipelined risc v processor. the pipelining technique is a fundamental concept in modern processor design, enabling improved instruction throughput and performance by overlapping instruction execution stages.

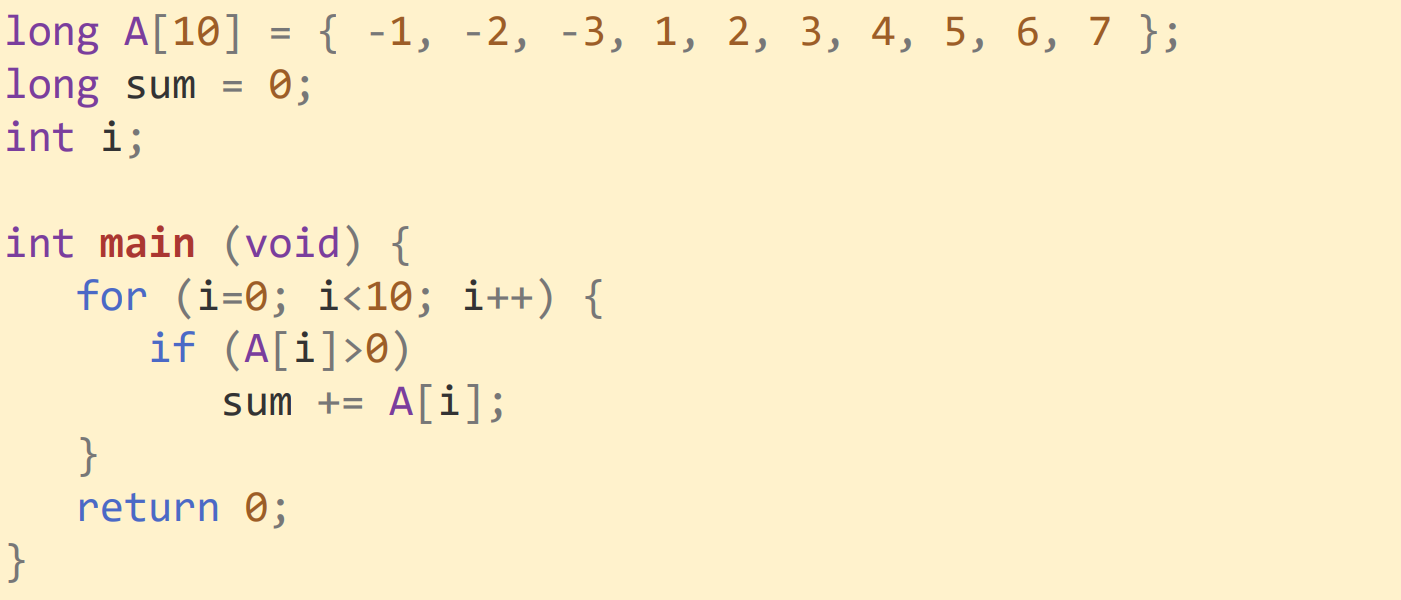

Github Taepoong719 Riscv Cpu Verilog Risc V Cpu Implemented By Verilog This is a verilog code for a 5 stage pipelined risc v processor with forwarding, stalling, and flushing functionality. here is the circuit diagramme of the processor. In this blog post, we will explore the implementation of a pipelined risc v processor using verilog, a hardware description language. Five stage risc v 32i pipelined cpu implementation on fpga with uart and visualization tools. Based on rv32i, the design and verification of a 5 stage pipelined risc processor, incorporating 20 instructions across various types and considering future enhancements such as branch prediction and data forwarding, represents a comprehensive approach to processor development.

Github Eumendies Riscv Pipeline Cpu Verilog Risc V Pipeline Cpu Core Five stage risc v 32i pipelined cpu implementation on fpga with uart and visualization tools. Based on rv32i, the design and verification of a 5 stage pipelined risc processor, incorporating 20 instructions across various types and considering future enhancements such as branch prediction and data forwarding, represents a comprehensive approach to processor development. The following is a verilog code implementation of a 5 stage pipeline risc v cpu. this cpu architecture is designed to execute instructions in a pipelined manner, allowing for improved performance and efficiency. With the help of the required block diagrams, we also built this processor with five levels of pipelining, each of which has a detailed description of its operation. this project uses verilog to develop and simulate a risc v. This article uses verilog to design a 5 stage pipeline cpu based on risc v architecture in vivado 2022.2. Ul architecture due to its simplicity, flexibility, and cost effectiveness. this paper presents the design and implementation of a 5 stage pipelined risc v processor based on the rv32i instruction set, optimizing processing.

Comments are closed.