Risc V Pipelined Datapath

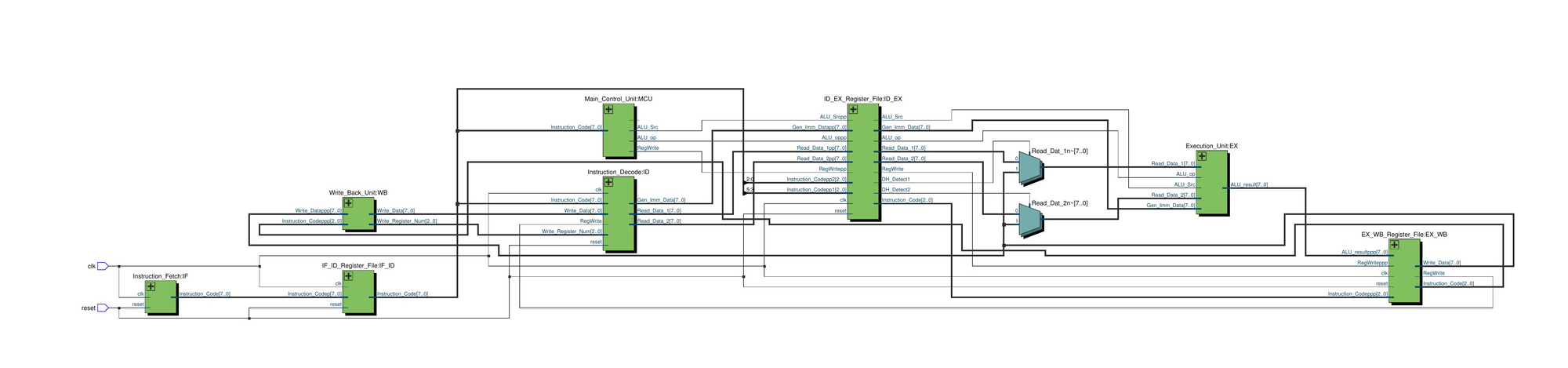

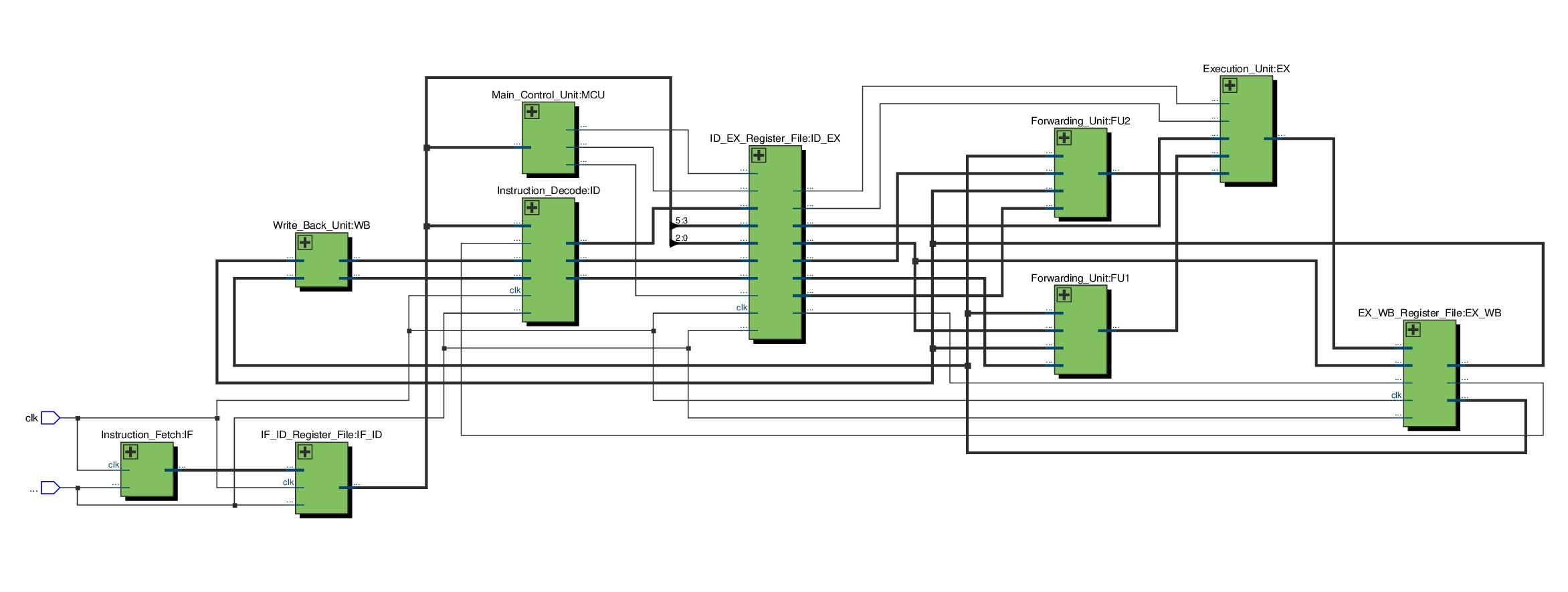

Risc V Datapath Summary Pdf Computer Architecture Office Equipment This repository contains the design and implementation of a 5 stage, in order, pipelined risc v processor datapath, written entirely in verilog. the design was functionally verified in simulation and validated on a pynq fpga platform. Webrisc v offers an online simulation platform for risc v pipelined datapath, enabling users to explore and understand its architecture and functionality.

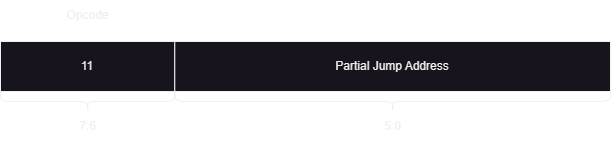

Risc V Pipelined Processor This project provides a clear and educational look into how a risc v–style processor operates internally. by modeling the datapath and pipeline stages explicitly, it serves as a foundation for deeper exploration into processor design, pipelining, and computer architecture. Explore risc v pipelining, datapath, and control in this computer organization lecture. covers instruction execution stages, pipeline hazards, and performance improvements. Cpu datapath, control intro design principles five steps to design a processor: analyze instruction set → datapath requirements select set of datapath components & establish clock methodology assemble datapath meeting the requirements. Webrisc v is a web based education oriented tool, which permits the investigation of the pipelined execution of assembly programs according to the rv32im and rv64im specifications (32 bit or 64 bit risc v processor).

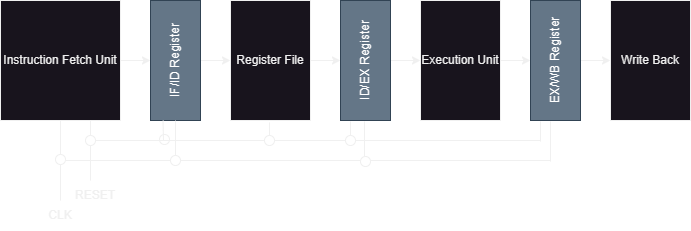

Risc V Pipelined Processor Cpu datapath, control intro design principles five steps to design a processor: analyze instruction set → datapath requirements select set of datapath components & establish clock methodology assemble datapath meeting the requirements. Webrisc v is a web based education oriented tool, which permits the investigation of the pipelined execution of assembly programs according to the rv32im and rv64im specifications (32 bit or 64 bit risc v processor). In this chapter we have seen that the risc v instruction set was designed with pipelining in mind. a datapath closely aligned by a 5 stage pipeline separating datapath components allows executing parts of multiple instructions simultaneously. A 5 stage pipeline will befocus of our detailed design some commercial designs have over 30 pipeline stages to do an integer add!. Toggle between the visualizations below to visualize the five stage pipelined datapath. at each rising clock edge, pipeline registers carry data and control signals to the next stage. This paper presents a methodology that uses a software development approach for designing processors in a higher programming language; chisel and demonstrates a completely open source route for.

Risc V Pipelined Processor In this chapter we have seen that the risc v instruction set was designed with pipelining in mind. a datapath closely aligned by a 5 stage pipeline separating datapath components allows executing parts of multiple instructions simultaneously. A 5 stage pipeline will befocus of our detailed design some commercial designs have over 30 pipeline stages to do an integer add!. Toggle between the visualizations below to visualize the five stage pipelined datapath. at each rising clock edge, pipeline registers carry data and control signals to the next stage. This paper presents a methodology that uses a software development approach for designing processors in a higher programming language; chisel and demonstrates a completely open source route for.

Risc V Pipelined Processor Toggle between the visualizations below to visualize the five stage pipelined datapath. at each rising clock edge, pipeline registers carry data and control signals to the next stage. This paper presents a methodology that uses a software development approach for designing processors in a higher programming language; chisel and demonstrates a completely open source route for.

Comments are closed.