Risc V Logisim Program Counter

Risc V Logisim Program Counter In this video, i use logisim to build a 32 bit program counter that will eventually be incorporated into an rv32i cpu that can be synthesized on to an fpga. Learn about the risc v instruction set architecture by building hardware. in this video, i use logisim to build a 32 bit program counter that will eventually be incorporated into an rv32i cpu that can.

Github Leijurv Logisim Risc V Unlike most other isa designs, the risc v isa is provided under open source licenses that do not require fees to use. this project focuses on making a risc v cpu core using logisim software. The program counter (pc), commonly called the instruction pointer (ip), and sometimes called the instruction address register (iar), the instruction counter, or just part of the instruction sequencer, is a processor register that indicates where a computer is in its program sequence. Risc v is ideal for a variety of applications from iots to embedded systems such as disks, cpus, calculators, socs, etc. risc v (reduced instruction set architecture) is an open standard instruction set architecture (isa) based on established reduced instruction set computer (risc) principles. It can do all of the basic risc v instructions including arithmetic as well as jal and branch type instructions. it also contains the keyboard and ttl components for io, as well as the interrupt controllers!.

Github Toms42 Logisim Risc V Cpu Risc v is ideal for a variety of applications from iots to embedded systems such as disks, cpus, calculators, socs, etc. risc v (reduced instruction set architecture) is an open standard instruction set architecture (isa) based on established reduced instruction set computer (risc) principles. It can do all of the basic risc v instructions including arithmetic as well as jal and branch type instructions. it also contains the keyboard and ttl components for io, as well as the interrupt controllers!. This document describes the implementation, function, and behavior of the program counter module in the architecture. for information about the instruction memory that the pc interfaces with, see instruction memory. In this project, we are using a 32 bit cpu, taking machine code instructions based on risc v. you can simply think of a machine, taking in a bunch of zeros'n'ones (or usually we take code in hexadecimal system). After seeing how simple risc v is that idea is pretty much scrapped for now. not to set my sights too high, but there is a small possibility of risk vee eventually being able to run the risc v port of linux. This was basically my first year cpu architecture course project, but in python and without the gui. really fun to program such things.

Github Javeria Batool7 Single Cycle Risc V Logisim This document describes the implementation, function, and behavior of the program counter module in the architecture. for information about the instruction memory that the pc interfaces with, see instruction memory. In this project, we are using a 32 bit cpu, taking machine code instructions based on risc v. you can simply think of a machine, taking in a bunch of zeros'n'ones (or usually we take code in hexadecimal system). After seeing how simple risc v is that idea is pretty much scrapped for now. not to set my sights too high, but there is a small possibility of risk vee eventually being able to run the risc v port of linux. This was basically my first year cpu architecture course project, but in python and without the gui. really fun to program such things.

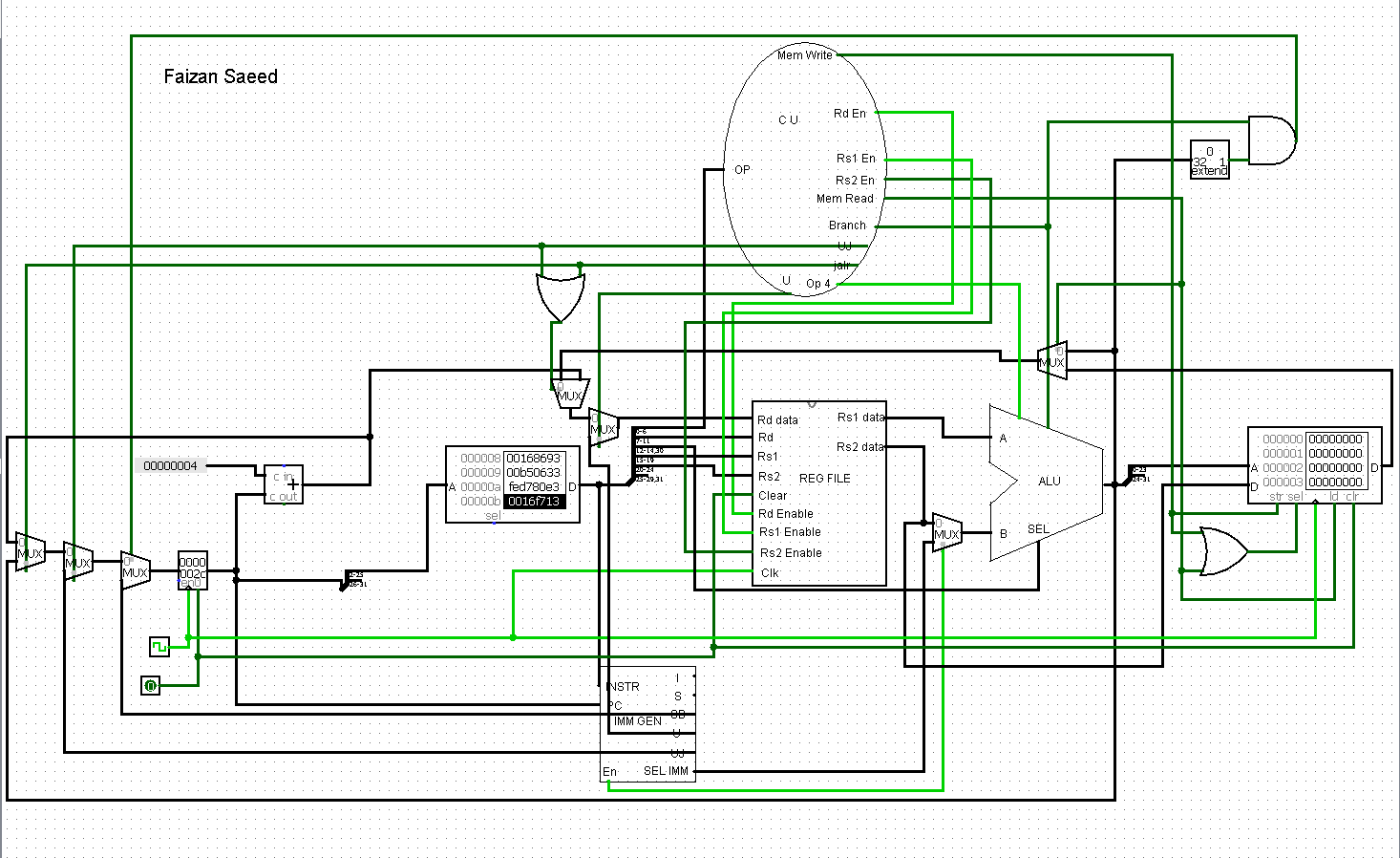

Github Fa1zansaeed Risc V Processor Simulate On Logisim After seeing how simple risc v is that idea is pretty much scrapped for now. not to set my sights too high, but there is a small possibility of risk vee eventually being able to run the risc v port of linux. This was basically my first year cpu architecture course project, but in python and without the gui. really fun to program such things.

Github Adeen317 Risc V 32 Bit Implementation On Logisim

Comments are closed.