Risc V Cpu

Risc V Cpu Risc v (pronounced "risk five") [3]: 1 is a free and open standard instruction set architecture (isa) based on reduced instruction set computer (risc) principles. Risc v is an open standard instruction set architecture (isa) enabling a new era of processor innovation through open collaboration.

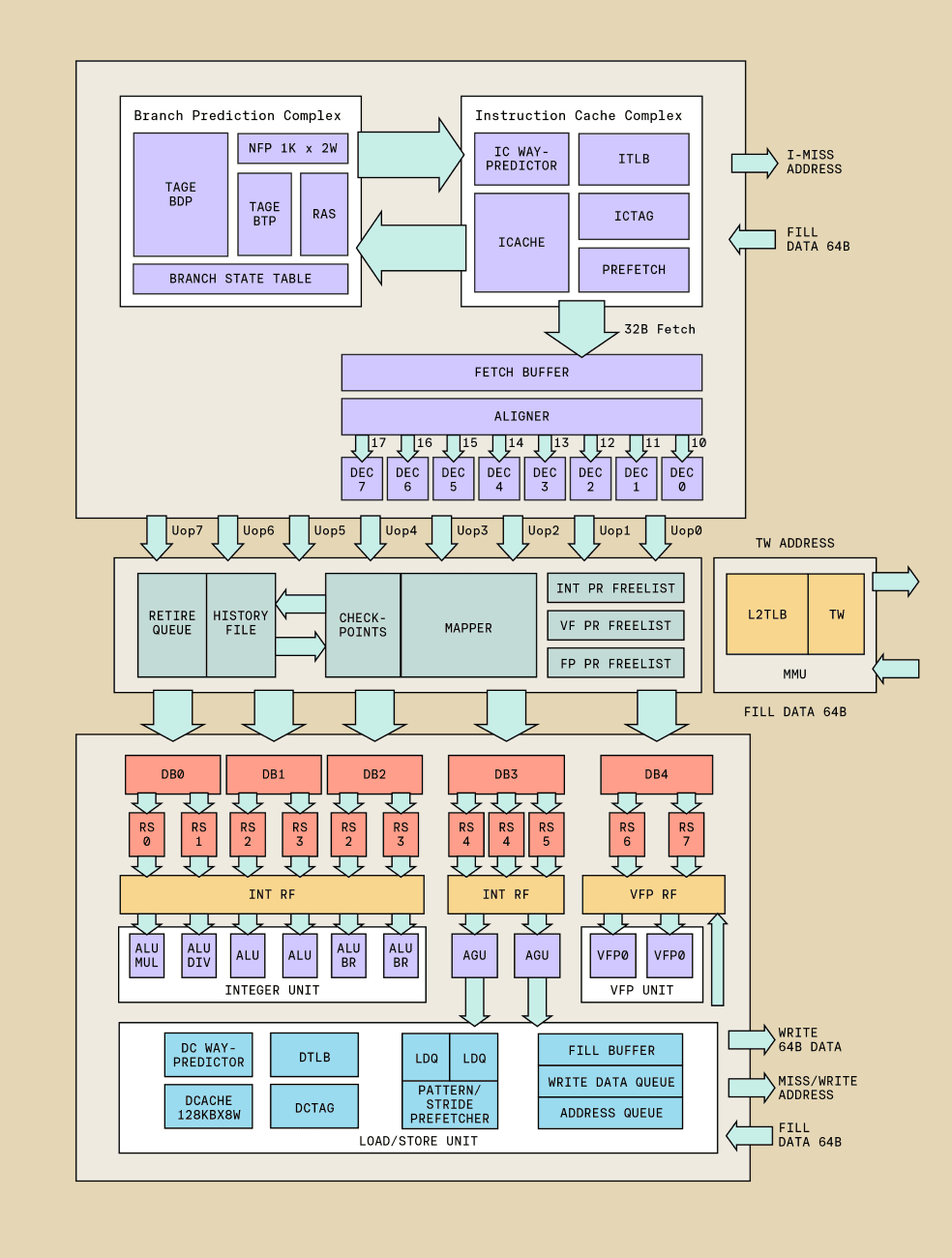

Risc V Cpu Discover everything that you need to know about risc v processors – starting from their history, how they work to their potential use cases. Learn about risc v, an open source instruction set architecture that executes few computer instructions and is extensible and customizable. see the features, pipeline, caches, and branch predictor of risc v processor and its history and uses. Risc v is an open source instruction set architecture used to develop custom processors for a variety of applications, from embedded designs to supercomputers. Risc v processor technical support and production for your commercial, industrial and military projects. the specifications shown below represent the current, ratified releases. work is being done on github. past ratified releases include the term “ratified” in the release tag.

Risc V Cpu Risc v is an open source instruction set architecture used to develop custom processors for a variety of applications, from embedded designs to supercomputers. Risc v processor technical support and production for your commercial, industrial and military projects. the specifications shown below represent the current, ratified releases. work is being done on github. past ratified releases include the term “ratified” in the release tag. Explore risc v, the revolutionary open source cpu architecture driving high performance computing, flexibility, and scalability across industries like automotive, consumer electronics, and data centers. Risc v is an open source instruction set architecture (isa) that rapidly transforms the cpu design and development landscape. unlike proprietary isas, risc v allows free access to architecture specifications, enabling the creation of custom processors tailored to specific needs without licensing fees. This article is a primer into the basics of risc v. the open architecture philosophy is exposed, along with a technical description of the modular isa, and some commercial risc v microprocessor implementations. Risc v is an open source isa used for processor development. based on the principles of reduced instruction set computing (risc), it provides a simple, clean design that enables efficient processor performance while fostering innovation through its open and modular architecture.

Github Liuxynb Risc V Cpu Design 计算机组原课设 Github Explore risc v, the revolutionary open source cpu architecture driving high performance computing, flexibility, and scalability across industries like automotive, consumer electronics, and data centers. Risc v is an open source instruction set architecture (isa) that rapidly transforms the cpu design and development landscape. unlike proprietary isas, risc v allows free access to architecture specifications, enabling the creation of custom processors tailored to specific needs without licensing fees. This article is a primer into the basics of risc v. the open architecture philosophy is exposed, along with a technical description of the modular isa, and some commercial risc v microprocessor implementations. Risc v is an open source isa used for processor development. based on the principles of reduced instruction set computing (risc), it provides a simple, clean design that enables efficient processor performance while fostering innovation through its open and modular architecture.

Risc V Cpu This article is a primer into the basics of risc v. the open architecture philosophy is exposed, along with a technical description of the modular isa, and some commercial risc v microprocessor implementations. Risc v is an open source isa used for processor development. based on the principles of reduced instruction set computing (risc), it provides a simple, clean design that enables efficient processor performance while fostering innovation through its open and modular architecture.

Risc V Cpu

Comments are closed.