Pdf Multi Level Logic Optimization

Pdf Multi Level Logic Optimization For Low Power Using Local Logic Three basic methods for multi level logic optimization, namely algebraic logic optimization, boolean logic optimization, and decomposition of boolean functions, are reviewed. To find an optimal multi level expression, we need to generate all possible divisors and choose an expression with the smallest number of literals.

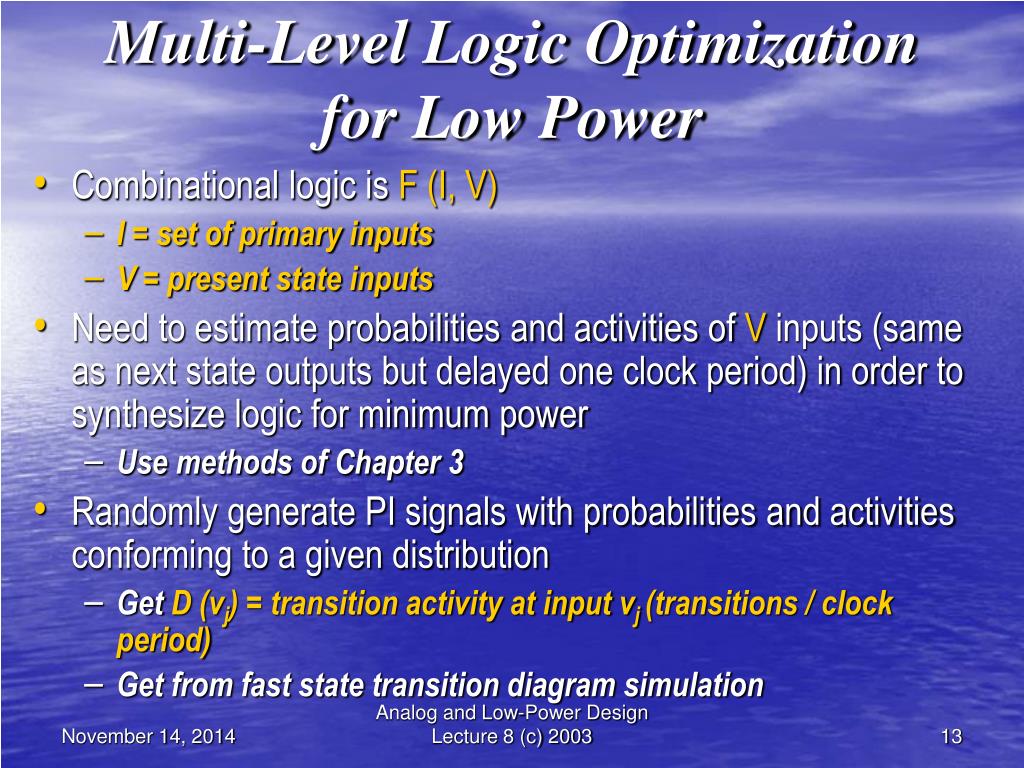

Ppt Logic Synthesis 3 Powerpoint Presentation Free Download Id 6097616 In this paper, we briefly present the major components of the multiple level logic optimization system. these include the input language, the global opti mization strategy for area minimization under timing constraints, and the local optimization step for mapping the resulting set of logic equations into an imple mentation. Modern approach to logic optimization divide logic optimization into two subproblems:. Factored forms are useful in estimating area and delay in a multi level synthesis and optimization system. in many design styles (e.g. complex gate cmos design) the implementation of a function corresponds directly to its factored form. ` logic optimization, a part of logic synthesis in electronics, is the process of finding an equivalent representation of the specified logic circuit under one or more specified constraints.

Pdf A Fast Algorithm For Three Level Logic Optimization Factored forms are useful in estimating area and delay in a multi level synthesis and optimization system. in many design styles (e.g. complex gate cmos design) the implementation of a function corresponds directly to its factored form. ` logic optimization, a part of logic synthesis in electronics, is the process of finding an equivalent representation of the specified logic circuit under one or more specified constraints. The document summarizes logic synthesis and multi level logic minimization. it discusses general logic structure, optimization criteria for synthesis including area, delay, testability, power, and placeability. Summary multi level logic synthesis is performed by step wise transformations algorithms are based on both the boolean and algebraic models rule based models. It produces a multilevel set of optimized logic equations preserving the input output behavior. the system includes both fast and slower (but more optimal) versions of algorithms for minimizing the area, and global timing optimization algorithms to meet system level timing constraints. Representation of a circuit to optimize independent of technology (65nm vs. 28nm, etc.) result of optimization can be evaluated effectively two (circuit) representations network representation (network graph).

Pdf Process Optimization Of Via Plug Multilevel Interconnections In The document summarizes logic synthesis and multi level logic minimization. it discusses general logic structure, optimization criteria for synthesis including area, delay, testability, power, and placeability. Summary multi level logic synthesis is performed by step wise transformations algorithms are based on both the boolean and algebraic models rule based models. It produces a multilevel set of optimized logic equations preserving the input output behavior. the system includes both fast and slower (but more optimal) versions of algorithms for minimizing the area, and global timing optimization algorithms to meet system level timing constraints. Representation of a circuit to optimize independent of technology (65nm vs. 28nm, etc.) result of optimization can be evaluated effectively two (circuit) representations network representation (network graph).

Multilevel Logic Optimization 1 Multilevel Logic Synthesis Two It produces a multilevel set of optimized logic equations preserving the input output behavior. the system includes both fast and slower (but more optimal) versions of algorithms for minimizing the area, and global timing optimization algorithms to meet system level timing constraints. Representation of a circuit to optimize independent of technology (65nm vs. 28nm, etc.) result of optimization can be evaluated effectively two (circuit) representations network representation (network graph).

Ppt Lecture 8 Logic Circuit Synthesis For Low Power Powerpoint

Comments are closed.