Pdf Fast Parallel Prefix Modulo 2 N 1 Adders

Design Of Parallel Prefix Adders Pdf Download Free Pdf Arithmetic In this paper, we present two novel architectures for designing modulo 2n 1 adders, based on parallel prefix carry computation units, the first architecture utilizes a fast carry. Abstract two architectures for modulo 2n 1 adders are introduced in this paper. the first one is built around a sparse carry computation unit that computes only some of the carries of the modulo 2n 1 addition.

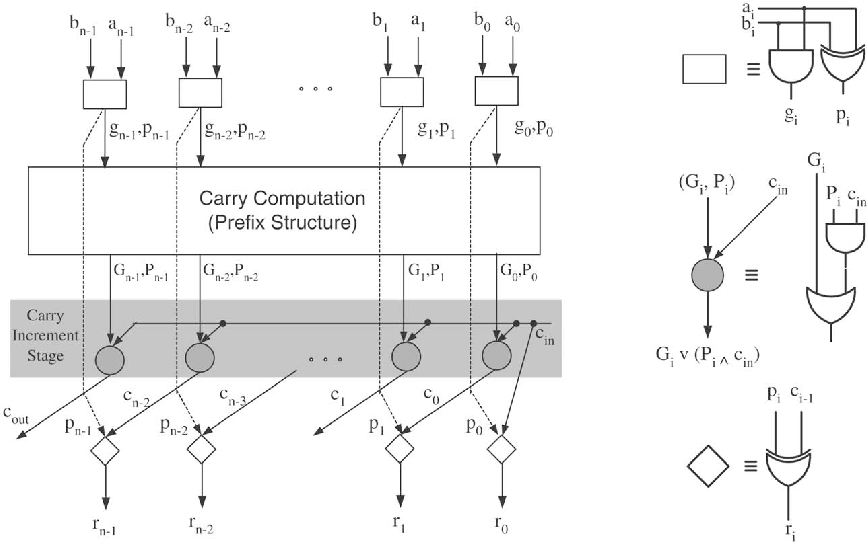

Parallel Prefix Binary Adder Iii Modulo 2 N 1 Adders Modulo 2 N 1 In this paper, we present two novel architectures for designing modulo 2 1 adders, based on parallel prefix carry computation units. our first architecture utilizes a fast carry increment stage, whereas the second is a totally parallel prefix solution. In this paper, we present two novel architectures for designing modulo 2^n 1 adders, based on parallel prefix carry computation units. the first architecture utilizes a fast carry increment stage, whereas the second is a totally parallel prefix solution. 1. introduction in floating point arithmetic [4]. many solutions have been presented for fast modulo 2n ¡ 1 addition. in [5] modulo adders are proposed that use a parallel prefix carry computation unit along with an extra prefix level. The parallel prefix formulation of binary addition is a very convenient way to formally describe an entire family of parallel binary adders. a novel architecture has been proposed that uses a sparse totally regular parallel prefix carry computation unit.

Figure 1 From Fast Parallel Prefix Modulo 2 Sup N 1 Adders Semantic 1. introduction in floating point arithmetic [4]. many solutions have been presented for fast modulo 2n ¡ 1 addition. in [5] modulo adders are proposed that use a parallel prefix carry computation unit along with an extra prefix level. The parallel prefix formulation of binary addition is a very convenient way to formally describe an entire family of parallel binary adders. a novel architecture has been proposed that uses a sparse totally regular parallel prefix carry computation unit. In this paper, we present two novel architectures for designing modulo 2^n 1 adders, based on parallel prefix carry computation units. the first architecture utilizes a fast carry increment stage, whereas the second is a totally parallel prefix solution. In this paper, we also present a novel architectures for designing modulo 2 n 1 adders, based on parallel prefix carry computation units. cmos implementations reveal the superiority of the resulting adders against previously reported solutions in terms of implementation area and delay. A novel parallel prefix architecture for high speed module 2 sup n 1 adders is presented, based on the idea of recirculating the generate and propagate signals, instead of the traditional end around carry approach. This architecture was derived by proving the inverted circular idem potency property of the parallel prefix carry operator in modulo 2n 1addition and by introducing a new prefix operator that eliminates the need for a double computation tree in the earlier fastest proposals.

Figure 3 From Fast Parallel Prefix Modulo 2 Sup N 1 Adders Semantic In this paper, we present two novel architectures for designing modulo 2^n 1 adders, based on parallel prefix carry computation units. the first architecture utilizes a fast carry increment stage, whereas the second is a totally parallel prefix solution. In this paper, we also present a novel architectures for designing modulo 2 n 1 adders, based on parallel prefix carry computation units. cmos implementations reveal the superiority of the resulting adders against previously reported solutions in terms of implementation area and delay. A novel parallel prefix architecture for high speed module 2 sup n 1 adders is presented, based on the idea of recirculating the generate and propagate signals, instead of the traditional end around carry approach. This architecture was derived by proving the inverted circular idem potency property of the parallel prefix carry operator in modulo 2n 1addition and by introducing a new prefix operator that eliminates the need for a double computation tree in the earlier fastest proposals.

Pdf Fast Parallel Prefix Modulo 2 N 1 Adders A novel parallel prefix architecture for high speed module 2 sup n 1 adders is presented, based on the idea of recirculating the generate and propagate signals, instead of the traditional end around carry approach. This architecture was derived by proving the inverted circular idem potency property of the parallel prefix carry operator in modulo 2n 1addition and by introducing a new prefix operator that eliminates the need for a double computation tree in the earlier fastest proposals.

Figure 3 From Fast Parallel Prefix Modulo 2 Sup N 1 Adders Semantic

Comments are closed.