Parity Generator And Checker Digital Electronics

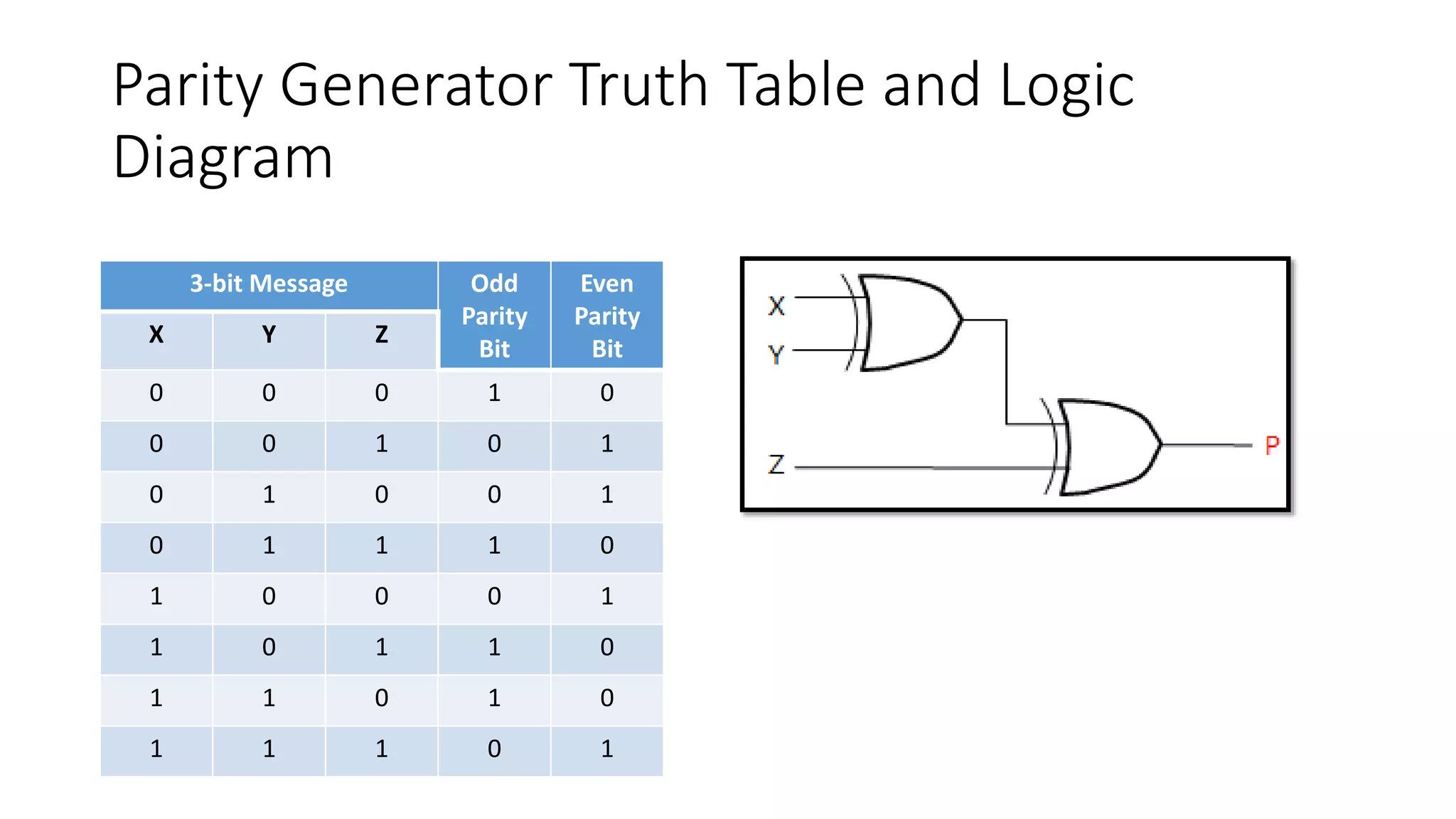

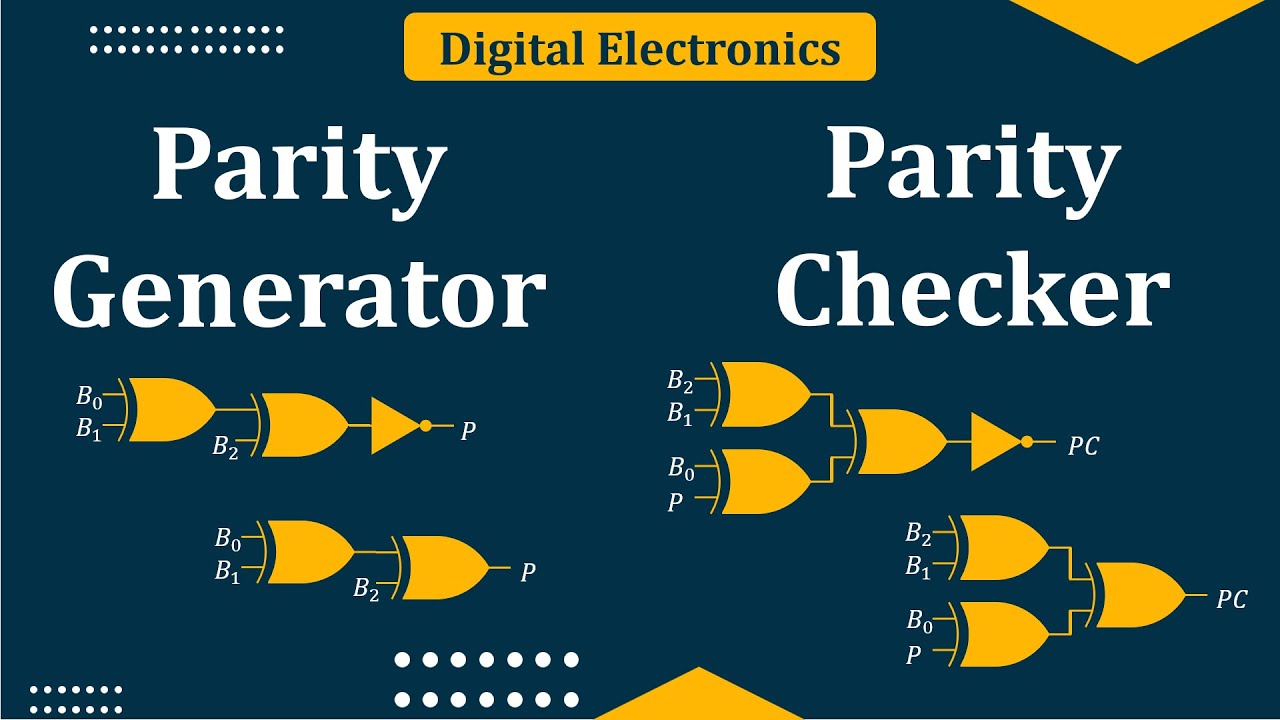

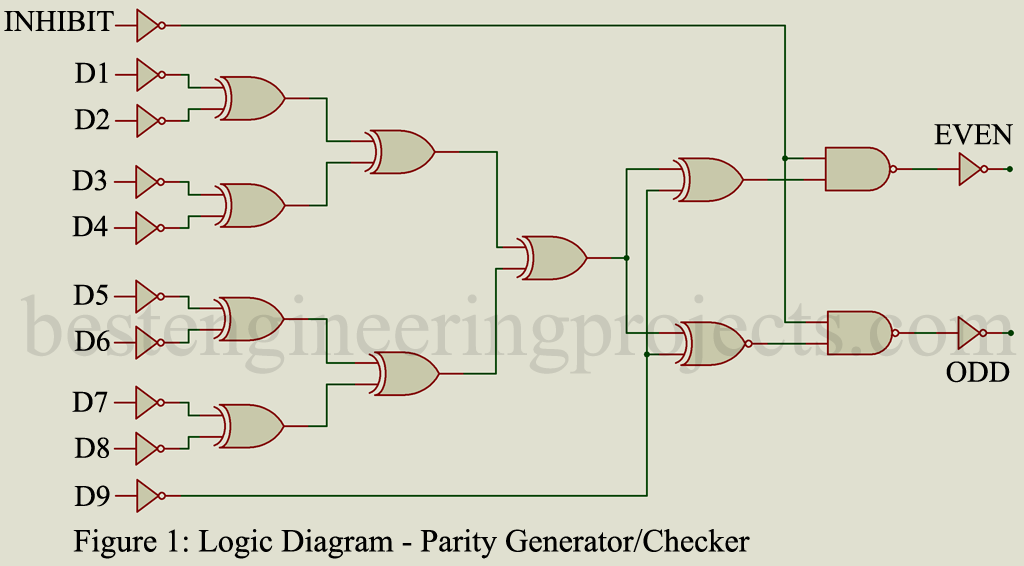

Parity Generator And Parity Checker Pptx A parity generator is a combinational logic circuit used to generate and add a parity to the input or transmitted data, while a parity checker is also a combinational circuit used to verify the correctness of received data. In implementing generator or checker circuits, unused parity bits must be tied to logic zero and the cascading inputs must not be equal. if this ic is used as an even parity checker and when a parity error occurs, the ‘sum even’ output goes low and ‘sum odd’ output goes high.

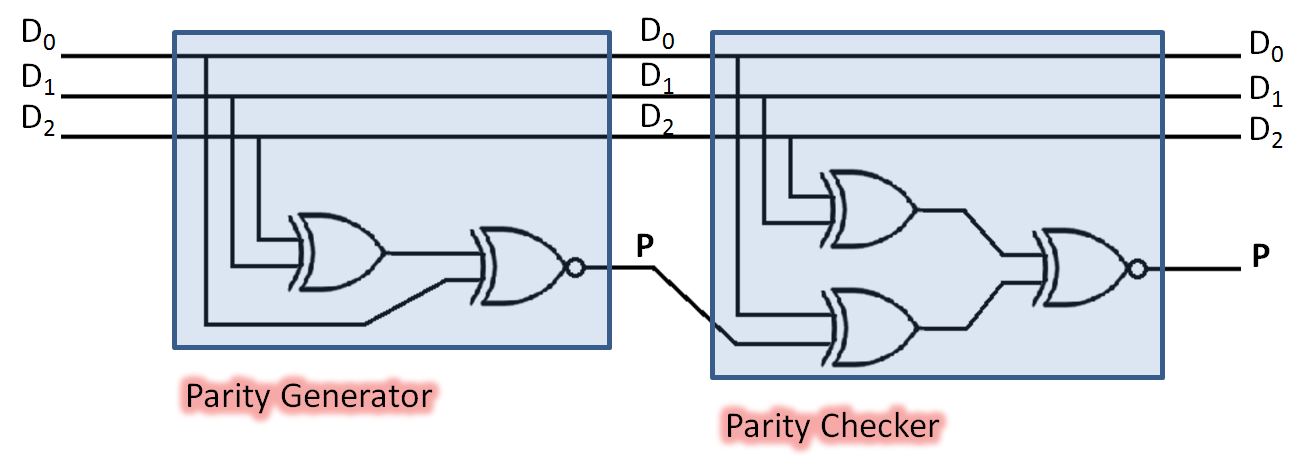

Parity Generator Parity Checker Parity Generator And Parity Checker Parity generators and checkers are devices that help ensure error free data transmission and processing in digital electronic systems. they use an extra bit, called a parity bit, to detect single bit errors that may occur due to noise or interference. A parity generator is a combinational logic circuit that generates the parity bit in the transmitter. on the other hand, a circuit that checks the parity in the receiver is called parity checker. What is the difference between the parity generator and parity checker? the parity generator generates the parity bit in the transmitter and the parity checker checks the parity bit in the receiver. The document explains the concepts of parity bits, parity generators, and parity checkers used in digital communication to detect errors during data transmission.

Parity Generator Checker Error Detector Engineering Projects What is the difference between the parity generator and parity checker? the parity generator generates the parity bit in the transmitter and the parity checker checks the parity bit in the receiver. The document explains the concepts of parity bits, parity generators, and parity checkers used in digital communication to detect errors during data transmission. Interactive visualization of parity generators and checkers in digital logic design with real time simulations for even and odd parity techniques. parity generators and checkers are fundamental components in digital systems used for error detection during data transmission. We need to add the parity bit to a signal. this is done by the parity generator. this parity inclusive binary message then transmits from transmitter to receiver end. the parity checker matches the number of 1’s at the receiver’s end with that of the transmitter’s end to check for errors. The parity bit is added to the message bits on the sender side to help in error detection at the receiver side. the binary message ensures an odd or even total of 1’s. To avoid problems caused by unwanted data corruption, a parity generator checker system, like the one shown in fig can be used. the basic idea is to add an extra bit, called a parity bit, to the digital information being transmitted.

Ppt Digital Systems Combinational Logic Circuits Powerpoint Interactive visualization of parity generators and checkers in digital logic design with real time simulations for even and odd parity techniques. parity generators and checkers are fundamental components in digital systems used for error detection during data transmission. We need to add the parity bit to a signal. this is done by the parity generator. this parity inclusive binary message then transmits from transmitter to receiver end. the parity checker matches the number of 1’s at the receiver’s end with that of the transmitter’s end to check for errors. The parity bit is added to the message bits on the sender side to help in error detection at the receiver side. the binary message ensures an odd or even total of 1’s. To avoid problems caused by unwanted data corruption, a parity generator checker system, like the one shown in fig can be used. the basic idea is to add an extra bit, called a parity bit, to the digital information being transmitted.

Digital Electronics Cmos To Lamp Interface Trader Wholesaler The parity bit is added to the message bits on the sender side to help in error detection at the receiver side. the binary message ensures an odd or even total of 1’s. To avoid problems caused by unwanted data corruption, a parity generator checker system, like the one shown in fig can be used. the basic idea is to add an extra bit, called a parity bit, to the digital information being transmitted.

Ourtutorials

Comments are closed.