Optimizing Sic Mosfet Module Paralleling Advanced Solutions And Best Practices Infineon

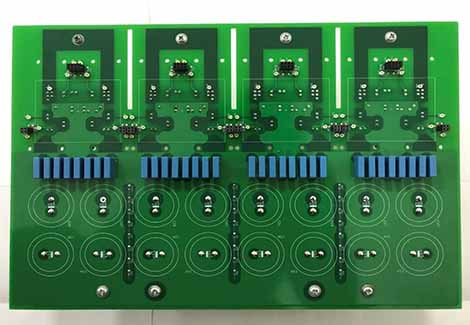

Paralleling Power Mosfets Pdf Mosfet Field Effect Transistor With sic mosfets, these challenges can be exacerbated due to the much faster device switching speeds. the goal of this paper is to show a practical design with four 6 mΩ 1200 v sic mosfet half bridge modules switching in hard parallel. Explore the key challenges and discover expert solutions for both gate driver and power layout design. uncover the significance of optimized system loop inductance in minimizing switching losses,.

Pdf 10 Kv Sic Mosfet Power Module With Reduced Common Mode 59 Off Paralleling must start with consideration of the module internal power and gate layout. the internal chip layout and module pin out can be designed to provide equal and symmetrical power and gate driver lay out for the multiple chips in parallel. Driving paralleled discrete coolsictm mosfets can be more complicated than driving single devices. along with switching losses or current imbalance, there can also be some severe oscillations. I'm reading through the paper from infineon title: a practical example of hard paralleling sic mosfet modules and have a couple questions regarding part selection of the design as shown in the paper below. Numerous efforts have been dedicated to analyzing and addressing the current imbalance issue of paralleling sic devices. this article comprehensively summarizes and presents state of the art research regarding the current imbalance in paralleled sic devices.

Paralleling Sic Mosfet Modules I'm reading through the paper from infineon title: a practical example of hard paralleling sic mosfet modules and have a couple questions regarding part selection of the design as shown in the paper below. Numerous efforts have been dedicated to analyzing and addressing the current imbalance issue of paralleling sic devices. this article comprehensively summarizes and presents state of the art research regarding the current imbalance in paralleled sic devices. Learn more about our silicon carbide (sic) coolsic™ mosfets—our solutions enable new levels of efficiency and system flexibility. Sic mosfet is the first device to face the below challenge for paralleling application:. When power semiconductor modules are connected in parallel, the switching characteristics and current imbalance of each device need to be aligned. this paper fo. This article is focusing on the challenges of paralleling of power mosfets in the non ideal layout in power converter application and the different methodology to resolve the current imbalance to achieve high performance of the converter.

Hard Paralleling Sic Mosfet Based Power Modules Timestech Learn more about our silicon carbide (sic) coolsic™ mosfets—our solutions enable new levels of efficiency and system flexibility. Sic mosfet is the first device to face the below challenge for paralleling application:. When power semiconductor modules are connected in parallel, the switching characteristics and current imbalance of each device need to be aligned. this paper fo. This article is focusing on the challenges of paralleling of power mosfets in the non ideal layout in power converter application and the different methodology to resolve the current imbalance to achieve high performance of the converter.

Hard Paralleling Sic Mosfet Based Power Modules Timestech When power semiconductor modules are connected in parallel, the switching characteristics and current imbalance of each device need to be aligned. this paper fo. This article is focusing on the challenges of paralleling of power mosfets in the non ideal layout in power converter application and the different methodology to resolve the current imbalance to achieve high performance of the converter.

Comments are closed.