Opb Ip Dev Process

Opb Pdf This 8 min video unpacks the unique thorough way we approach ip development. to talk about your project or for a quote email our creative director at shaddy@onepixelbrush more. In this 17 min episode we break down the arduous process we go through to try to get complex narratives to read while still maintining an impactful image that pushes well beyond just showing a cool environment.

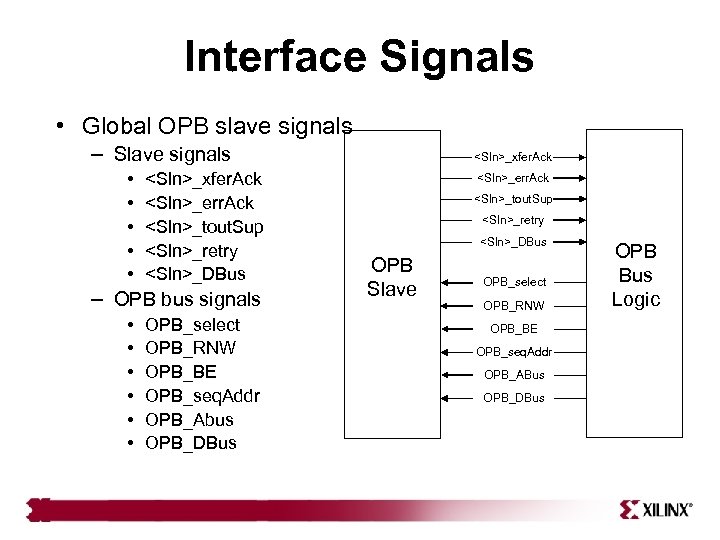

Opb Pdf In other words helping you make your idea from scratch this video gives an overview how we approached ip development with diaboli and outlining how it's an ongoing conversation between story tone and (if it's a game) gameplay watch?v=2fwjvqd4cnu&t=505s. The document outlines the process for choosing the required opb ipif services to interface the user logic to the opb bus without having to create all the provided ipif services. Here we attempt to nudge it a bit further in our original game ip diaboli. gore for gore's sake has no place but for a few seconds seeing the physical horrors of what's going on is important to understand the stakes of the story. The opb to pci 32 33 bridge is offered as an evaluation core in the edk. to generate a full opb to pci license, the pci 32 logicore must be purchased. the opb ipif v3 pci core bridge design bridges the opb ipif (on chip peripheral bus intellectual property interface) and the pci64 interface v3.0 core providing full bridge functionality between the xilinx 32 bit opb and a 32 bit v2.2 compliant.

Op Dev Procedure Pdf Here we attempt to nudge it a bit further in our original game ip diaboli. gore for gore's sake has no place but for a few seconds seeing the physical horrors of what's going on is important to understand the stakes of the story. The opb to pci 32 33 bridge is offered as an evaluation core in the edk. to generate a full opb to pci license, the pci 32 logicore must be purchased. the opb ipif v3 pci core bridge design bridges the opb ipif (on chip peripheral bus intellectual property interface) and the pci64 interface v3.0 core providing full bridge functionality between the xilinx 32 bit opb and a 32 bit v2.2 compliant. Hello all, i want to create an ip master on the opb. i am using xilinx virtex2 (xc2v2000), and xilinx platform studio (edk) version 7.1.02i on the xilinx multimedia board. i have tried looking everywhere for my answer and after a week of time well experienced i decided to ask the experts. The document outlines the process for choosing the required opb ipif services to interface the user logic to the opb bus without having to create all the provided ipif services. This document describes how to create and add a custom ip core to the on chip peripheral bus (opb) within edk xps. the custom ip core that we will generate is a very simple device consisting of a single control register and 4 general purpose registers. This ip core is one of more than 20 ip cores that are part of the embedded development kit. the opb to pci™ 32 33 bridge is offered as an evaluation core in the edk™.

Ip Op Design Pdf Input Output Databases Hello all, i want to create an ip master on the opb. i am using xilinx virtex2 (xc2v2000), and xilinx platform studio (edk) version 7.1.02i on the xilinx multimedia board. i have tried looking everywhere for my answer and after a week of time well experienced i decided to ask the experts. The document outlines the process for choosing the required opb ipif services to interface the user logic to the opb bus without having to create all the provided ipif services. This document describes how to create and add a custom ip core to the on chip peripheral bus (opb) within edk xps. the custom ip core that we will generate is a very simple device consisting of a single control register and 4 general purpose registers. This ip core is one of more than 20 ip cores that are part of the embedded development kit. the opb to pci™ 32 33 bridge is offered as an evaluation core in the edk™.

Adding Your Own Ip To The Opb Bus This document describes how to create and add a custom ip core to the on chip peripheral bus (opb) within edk xps. the custom ip core that we will generate is a very simple device consisting of a single control register and 4 general purpose registers. This ip core is one of more than 20 ip cores that are part of the embedded development kit. the opb to pci™ 32 33 bridge is offered as an evaluation core in the edk™.

Adding Your Own Ip To The Opb Bus

Comments are closed.