N Bit Ring Counter Made Using Vhdl

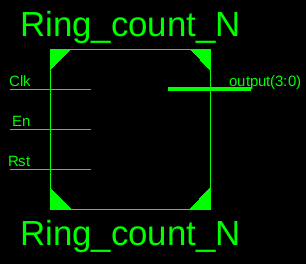

Vhdl Code For 4 Bit Ring Counter And Johnson Counter Pdf Vhdl I am going to design a n bit ring counter in vhdl. only just a single bit ‘1’ is revolved around ‘0’. bit is forwarded or shifted on each clock cycle. reset and enable is also part of the project. reset is active high and enable is also active high. both reset and enable are synchronous. This vhdl project is to implement a parameterized n bit switch tail ring counter using vhdl. vhdl code for parameterized ring counter is presented in this project.

N Bit Ring Counter Made Using Vhdl N bit ring counter (vhdl) overview this project implements a parameterizable n bit ring counter in vhdl. it was developed as part of the "advanced digital systems" course for a master's program. the design is suitable for fpga implementation and simulation. In this part of the vhdl cpld course, a ring counter is written in vhdl and then implemented on a cpld. this tutorial is also used to demonstrate the use of the vhdl ror and rol operators. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Explore counter design in vhdl for digital applications, covering synchronous, asynchronous, up, down, and up down counters.

N Bit Ring Counter Made Using Vhdl Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Explore counter design in vhdl for digital applications, covering synchronous, asynchronous, up, down, and up down counters. Vhdl code for ring counter ring counter vhdl code ring counter library ieee; use ieee.std logic 1164.all; entity ring counter is port ( clk : in std logic; reset : in std logic; output : out std logic vector (3 downto 0)); end ring counter; architecture behavioral of ring counter is signal temp : std logic vector (3 downto 0):= (others => '0. It is also known as a switch tail ring counter, walking ring counter, or johnson counter. it connects the complement of the output of the last shift register to the input of the first register and circulates a stream of ones followed by zeros around the ring. The document contains vhdl code for various digital circuits, including a bit counter, d flip flop, ring counter, and johnson counter. each section defines the entity and architecture for the respective components, detailing their input and output ports along with the logic for state changes. Vhdl counters last updated 1 9 25 counters used as individual blocks used inside a block timers – delays, time out,.

N Bit Ring Counter Made Using Vhdl Vhdl code for ring counter ring counter vhdl code ring counter library ieee; use ieee.std logic 1164.all; entity ring counter is port ( clk : in std logic; reset : in std logic; output : out std logic vector (3 downto 0)); end ring counter; architecture behavioral of ring counter is signal temp : std logic vector (3 downto 0):= (others => '0. It is also known as a switch tail ring counter, walking ring counter, or johnson counter. it connects the complement of the output of the last shift register to the input of the first register and circulates a stream of ones followed by zeros around the ring. The document contains vhdl code for various digital circuits, including a bit counter, d flip flop, ring counter, and johnson counter. each section defines the entity and architecture for the respective components, detailing their input and output ports along with the logic for state changes. Vhdl counters last updated 1 9 25 counters used as individual blocks used inside a block timers – delays, time out,.

Comments are closed.