Multisim Live Flipflop Issue

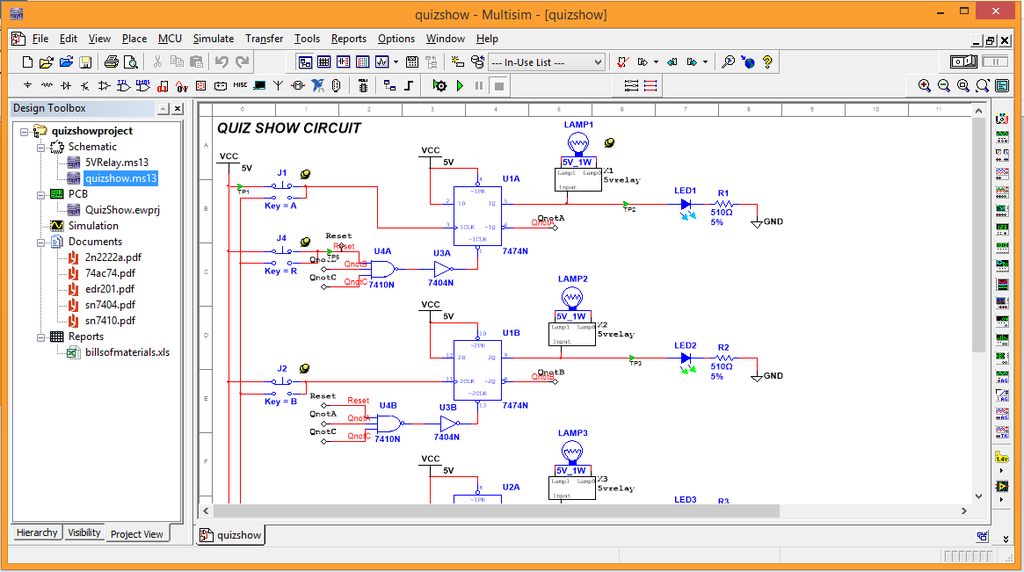

D Flipflop 1 Multisim Live Multisim desktop seems to require a probe on a nand gate output (preferably at one of the q or qb flip flop outputs). placing a probe on either sn or rn breaks the results. multisim live gives the correct results in those exact same condition. In order to select this type of flip flop, the checkbox for clock is left empty while the checkbox for set reset needs to be checked (see the screenshot below).

Jk Flipflop Multisim Live Enjoy the videos and music you love, upload original content, and share it all with friends, family, and the world on . This section covers common pitfalls and recommended solutions when using multisim live. if an issue persists after you complete a troubleshooting procedure, contact support via the chat widget. This circuit is an interconnection of d and s r latches in master slave configuration. this results to a negative edge triggered d flip flop. this can be converted to a positive edge triggered flip flop by inserting an inverter at the clock (clk) input. This section covers common pitfalls and recommended solutions when using multisim live. if an issue persists after you complete a troubleshooting procedure, contact ni technical support or visit ni support.

Ma18 D Flipflop 2 Multisim Live This circuit is an interconnection of d and s r latches in master slave configuration. this results to a negative edge triggered d flip flop. this can be converted to a positive edge triggered flip flop by inserting an inverter at the clock (clk) input. This section covers common pitfalls and recommended solutions when using multisim live. if an issue persists after you complete a troubleshooting procedure, contact ni technical support or visit ni support. This document contains the multisim live known issues that were discovered before and since the release of multisim live. known issues are performance issues or technical bugs that ni has acknowledged exist within this version of the product. This is a modification of the circuit master slave d latch (edge triggered d flip flop). all four two input nand gates of the d latch were replaced by three input nand gates and the two input output nand gates of the s r latch were replaced by three input nand gates. If the problem persists please contact us on the digilent forums and our engineers will help you troubleshoot the issue. when posting on the forums, please include as much information as possible to help us reproduce the issue. Use the chrome™ browser to best experience multisim live. the “d flip flop” will store and output whatever logic level is applied to its data terminal so long as the clock input is high.

Sr Master Slave Flipflop Multisim Live This document contains the multisim live known issues that were discovered before and since the release of multisim live. known issues are performance issues or technical bugs that ni has acknowledged exist within this version of the product. This is a modification of the circuit master slave d latch (edge triggered d flip flop). all four two input nand gates of the d latch were replaced by three input nand gates and the two input output nand gates of the s r latch were replaced by three input nand gates. If the problem persists please contact us on the digilent forums and our engineers will help you troubleshoot the issue. when posting on the forums, please include as much information as possible to help us reproduce the issue. Use the chrome™ browser to best experience multisim live. the “d flip flop” will store and output whatever logic level is applied to its data terminal so long as the clock input is high.

Multisim Live If the problem persists please contact us on the digilent forums and our engineers will help you troubleshoot the issue. when posting on the forums, please include as much information as possible to help us reproduce the issue. Use the chrome™ browser to best experience multisim live. the “d flip flop” will store and output whatever logic level is applied to its data terminal so long as the clock input is high.

Comments are closed.