Multi Chip Packaging Technology

Multi Chip Packaging Technology In this paper, developments in advanced packaging have been discussed, such as 3d ic packaging, fan out packaging, and chiplet packaging. insights on the major advantages and challenges have also been briefly introduced. Mcm technology emerged in the late 1980s as a response to the limitations of traditional single chip packaging approaches. this technology enables the integration of multiple bare dies or packaged components onto a single substrate, creating a unified module that functions as a complete subsystem.

Semiconductor Chip Packaging Technology Stable Diffusion Online These assemblies are best developed using fan out panel level packaging, replacing today’s wafer carrier with a panel. fan out packaging enables substantially lower cost than silicon interposers, while accommodating extra large die sizes with high i o counts. But rather than try to squeeze additional transistors onto a single chip, advanced multichip packaging enables the combining of smaller, cost and performance optimized dies—the unpackaged semiconductor chips comprised of functional integrated circuits. The development of advanced semiconductor packaging is focused on achieving high density integration, superior performance, efficient thermal management, high r. This chapter presents details of mcm technology, including different types, basic design rules, fundamental applications, and packaging alternatives to the mcm.

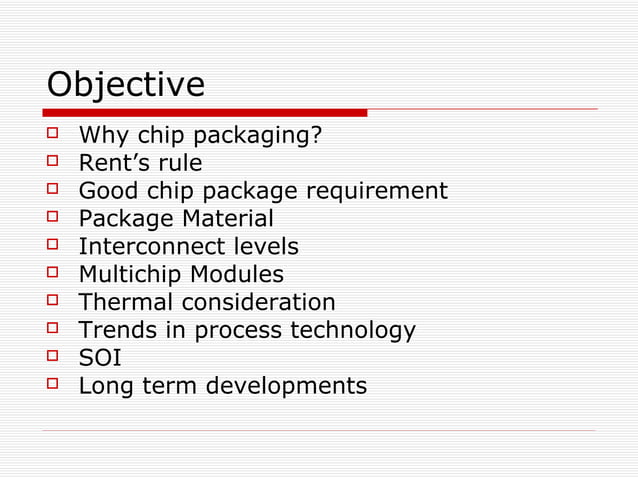

Chip Packaging Technology Ppt The development of advanced semiconductor packaging is focused on achieving high density integration, superior performance, efficient thermal management, high r. This chapter presents details of mcm technology, including different types, basic design rules, fundamental applications, and packaging alternatives to the mcm. The package technologies include substrate based technologies, redistribution layer (rdl), silicon interposer based and 3d stacking based packaging technologies. The iedm 2024 conference clearly demonstrated the increasing reliance on advanced packaging, specifically multi chip module integration and chiplet technology, across the semiconductor industry. A multi chip module (mcm) is an advanced electronic packaging technology that integrates multiple bare chips, semiconductor wafers, and other discrete components within a single package. this technology allows an mcm to function as a larger integrated circuit when in use. 3d packaging involves stacking multiple chips (face down) together, directly using through silicon vias to stack them vertically, linking the electronic signals of different chips above and below, achieving true vertical packaging.

Chip Packaging Technology Ppt The package technologies include substrate based technologies, redistribution layer (rdl), silicon interposer based and 3d stacking based packaging technologies. The iedm 2024 conference clearly demonstrated the increasing reliance on advanced packaging, specifically multi chip module integration and chiplet technology, across the semiconductor industry. A multi chip module (mcm) is an advanced electronic packaging technology that integrates multiple bare chips, semiconductor wafers, and other discrete components within a single package. this technology allows an mcm to function as a larger integrated circuit when in use. 3d packaging involves stacking multiple chips (face down) together, directly using through silicon vias to stack them vertically, linking the electronic signals of different chips above and below, achieving true vertical packaging.

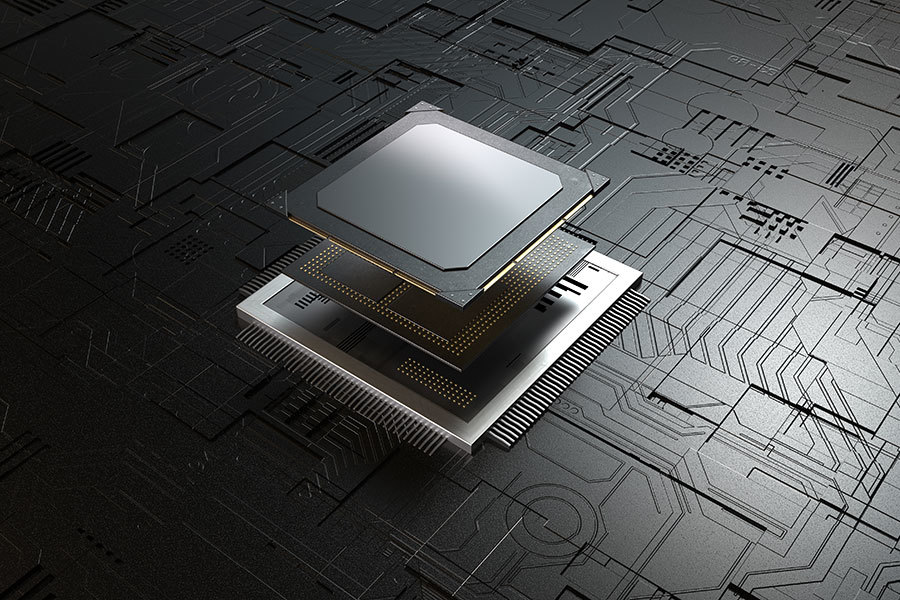

Chip Packaging Technology Ppt A multi chip module (mcm) is an advanced electronic packaging technology that integrates multiple bare chips, semiconductor wafers, and other discrete components within a single package. this technology allows an mcm to function as a larger integrated circuit when in use. 3d packaging involves stacking multiple chips (face down) together, directly using through silicon vias to stack them vertically, linking the electronic signals of different chips above and below, achieving true vertical packaging.

Comments are closed.