Logic Synthesis Explained Eda For Chip Design

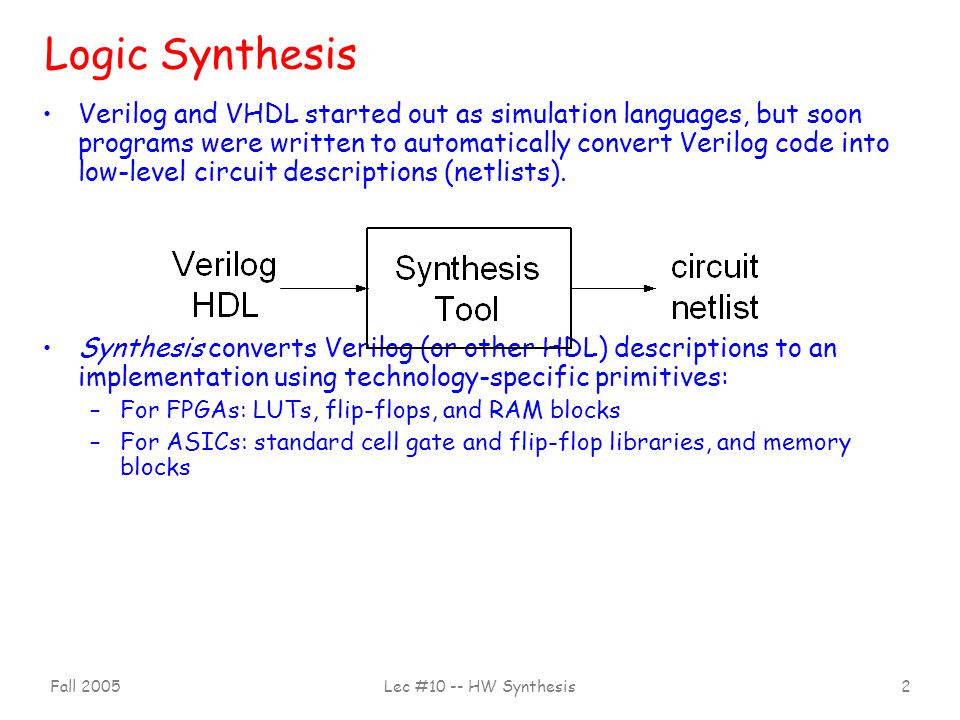

Eda Lecture Logic Synthesis Pdf Logic Synthesis Computer Engineering Logic synthesis: converts hardware functionality described in high level languages such as verilog or vhdl into an equivalent logic netlist. the logic synthesis stage performs logic optimization, generates placement constraints, and supports clock tree synthesis. Learn about logic synthesis, a crucial step in semiconductor chip design. understand how rtl code is transformed into optimized logic gates using eda tools l.

01 Intro Eda Software Pdf Logic Synthesis Logic Gate In the early stages of the development of logic synthesis, engineers used to design and optimize electronic circuits using pen and paper (the traditional method) and would do the iterations of the truth table with the help of karnaugh maps. Logic synthesis & verification .logic synthesis programs transform boolean expressions or register transfer level (rtl) description (in verilog vhdl c) into logic gate networks (netlist) in a particular library. Synthesis, within the field of electronic design automation (eda), is the automated process of transforming high level hardware descriptions into lower level representations that can be physically manufactured on a semiconductor chip. We have proposed multiple algorithms based on the xor and inverter graph (xaig) providing a solid logic synthesis framework capable of leveraging the logic primitives of sfq circuits and addressing technology specific sfq quality metrics early on in the eda flow.

Asic System On Chip Vlsi Design Asic Synthesis Synthesis 42 Off Synthesis, within the field of electronic design automation (eda), is the automated process of transforming high level hardware descriptions into lower level representations that can be physically manufactured on a semiconductor chip. We have proposed multiple algorithms based on the xor and inverter graph (xaig) providing a solid logic synthesis framework capable of leveraging the logic primitives of sfq circuits and addressing technology specific sfq quality metrics early on in the eda flow. Moreover, the synergy with technology mapping, physical design, verification, and test ensures a fully integrated electronic design automation (eda) stack, making logic synthesis a foundational step in the semiconductor design process. It covers topics including logic synthesis, simulation of digital circuits, and important symbols. logic synthesis topics include binary boolean functions, optimization of combinational and sequential circuits, and technology mapping. Logic synthesis is the automated process in electronic design automation (eda) that transforms a high level hardware description, typically in register transfer level (rtl) languages such as verilog or vhdl, into an optimized gate level netlist suitable for semiconductor chip implementation. The main research and development focus of the ieda research group is on the chip logic synthesis, physical design, sign off analysis and physical verification links, as shown in the green part of the following figure:.

Types Of Eda Synthesis And Logic Synthesis Principles Moreover, the synergy with technology mapping, physical design, verification, and test ensures a fully integrated electronic design automation (eda) stack, making logic synthesis a foundational step in the semiconductor design process. It covers topics including logic synthesis, simulation of digital circuits, and important symbols. logic synthesis topics include binary boolean functions, optimization of combinational and sequential circuits, and technology mapping. Logic synthesis is the automated process in electronic design automation (eda) that transforms a high level hardware description, typically in register transfer level (rtl) languages such as verilog or vhdl, into an optimized gate level netlist suitable for semiconductor chip implementation. The main research and development focus of the ieda research group is on the chip logic synthesis, physical design, sign off analysis and physical verification links, as shown in the green part of the following figure:.

Comments are closed.