Layout Of Sram

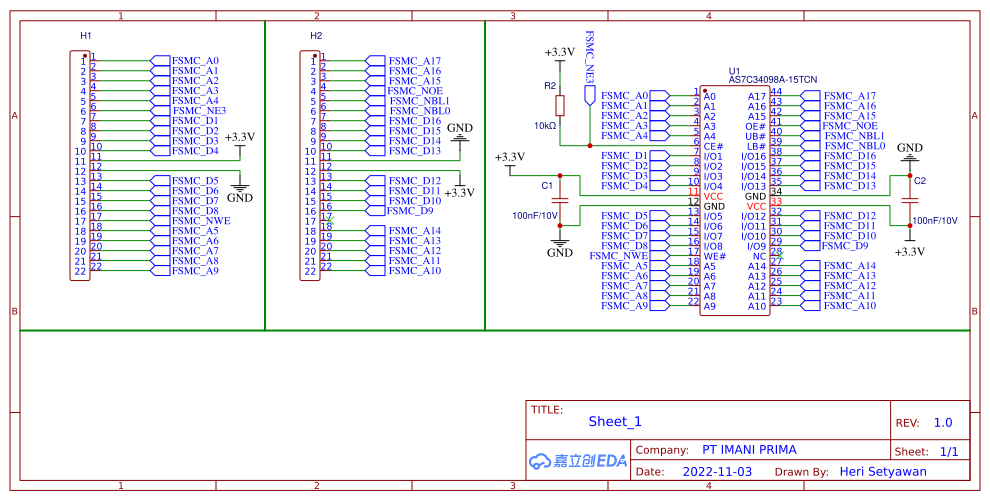

Layout Sram Easyeda Open Source Hardware Lab Abstract this paper presents a full custom memory layout design of 1kb sram, followed by physical verification checks, such as drc and lvs to validate the layouts implemented. Sram layout cell size is critical: 26 x 45 (even smaller in industry) tile cells sharing vdd, gnd, bitline contacts.

Layout Sram Easyeda Open Source Hardware Lab A 6t sram cell layout and array design was proposed. 6t sram are the most widely used memory cells due to their compact size and efficiency. the w l ratio of the transistors in sram cell impact the stability. Six layout variations of the 6t sram cell are examined and compared. the comparison includes four conventional cells, plus the thin cell commonly used in industry and a recently proposed ultra. In this paper, the design principles of sram including the peripheral circuitry, operations, challenges, mitigation techniques, how to improve the stability were clearly explained in a very simplified manner including the design schematic to show the memory cell and logic gates of the sram block. The document describes the design and implementation of a static ram (sram) cell using mentor graphics tools. it provides details on: 1) the typical structure of an sram cell, which uses six transistors arranged in two cross coupled inverters and two access transistors to store each bit.

31 10t Sram Cell Layout Download Scientific Diagram In this paper, the design principles of sram including the peripheral circuitry, operations, challenges, mitigation techniques, how to improve the stability were clearly explained in a very simplified manner including the design schematic to show the memory cell and logic gates of the sram block. The document describes the design and implementation of a static ram (sram) cell using mentor graphics tools. it provides details on: 1) the typical structure of an sram cell, which uses six transistors arranged in two cross coupled inverters and two access transistors to store each bit. Layout design: in this stage, the physical layout of the sram memory array is designed. this involves placing the individual circuits on the chip, routing the interconnections between the circuits, and optimizing the layout for performance and reliability. The article discusses the possibilities of physical design of the most common 6t memory cell of modern sram devices and the physical design of 16 bit and 256 bi. Explore sram memory architecture, including its structure, components, and working principles. learn how sram is used in modern chip design for fast and efficient memory storage. The document outlines the design and layout of a 128 word sram using the ibm 130nm process, focusing on key design tools and circuit components such as sram cells, precharge circuits, clock drivers, sense amplifiers, row and column decoders, and write drivers.

Standard 6t Sram Cell Layout Download Scientific Diagram Layout design: in this stage, the physical layout of the sram memory array is designed. this involves placing the individual circuits on the chip, routing the interconnections between the circuits, and optimizing the layout for performance and reliability. The article discusses the possibilities of physical design of the most common 6t memory cell of modern sram devices and the physical design of 16 bit and 256 bi. Explore sram memory architecture, including its structure, components, and working principles. learn how sram is used in modern chip design for fast and efficient memory storage. The document outlines the design and layout of a 128 word sram using the ibm 130nm process, focusing on key design tools and circuit components such as sram cells, precharge circuits, clock drivers, sense amplifiers, row and column decoders, and write drivers.

Comments are closed.