L10 3 Pipelined Datapath

Ppt A Pipelined Datapath Powerpoint Presentation Free Download Id Pipelining the datapath; inter stage registers; stage wise operation; pipeline diagrams; hardware utilization more. The document discusses the five stage pipelined datapath and illustrates instruction processing stages for various operations, including load and store instructions.

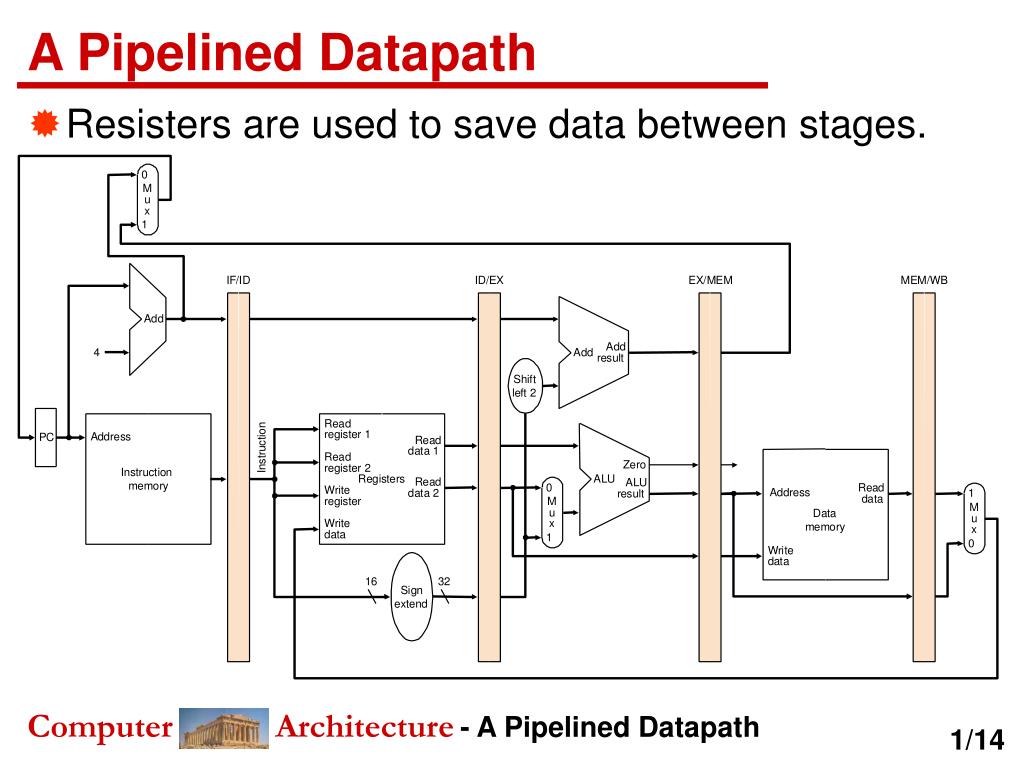

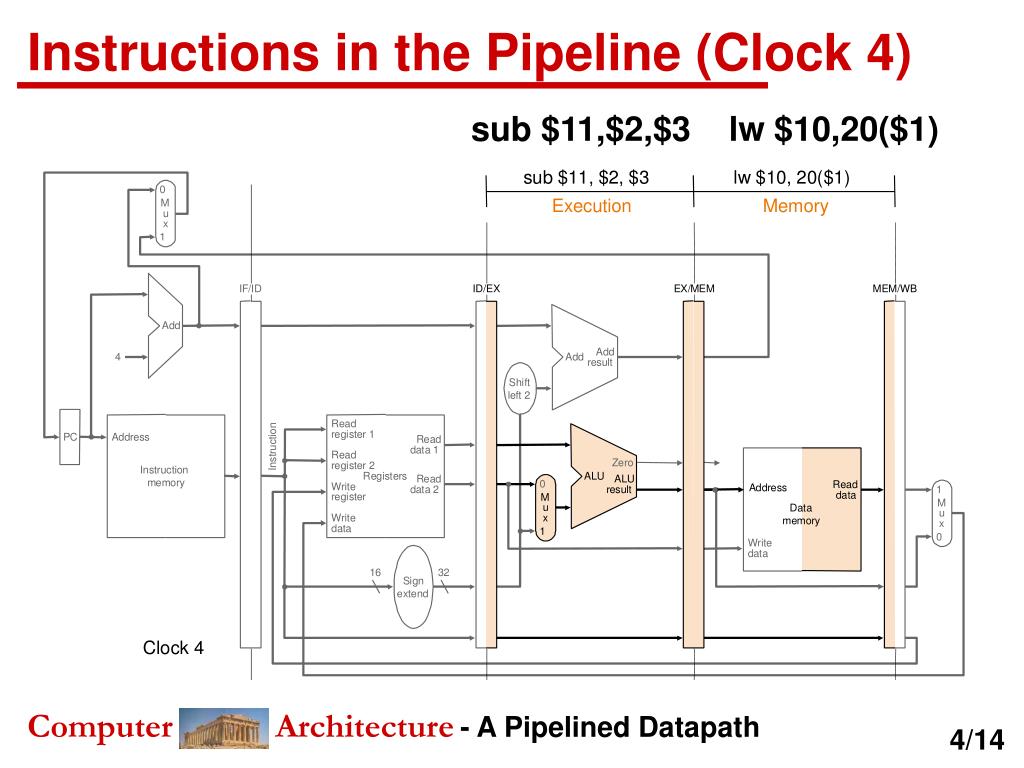

Ppt A Pipelined Datapath Powerpoint Presentation Free Download Id Nto a 32 b result. let’s walk through the datapath using the load word instruction as an example. load word is a good instruction to start with because it is active in every stage of the pipelined datapath. note that in the following datapaths, the right half of registers or memory are. Multiple clock cycle pipeline diagrams : shows the complete execution of instructions in a single figure. instruction order is from top to bottom, and clock cycles move from left to right. About pipeline speedup if all stages are balanced, i.e. all take the same time time between instructions (pipelined) = time between instructions (non pipelined) # of stages if not balanced, speedup will be less speedup is due to increased throughput, but instruction latency does not change. Data paths are essential parts of the computer architecture that work in a processor to execute instructions. there are two basic categorized methodologies in datapath design: multi cycle data paths and pipeline data paths.

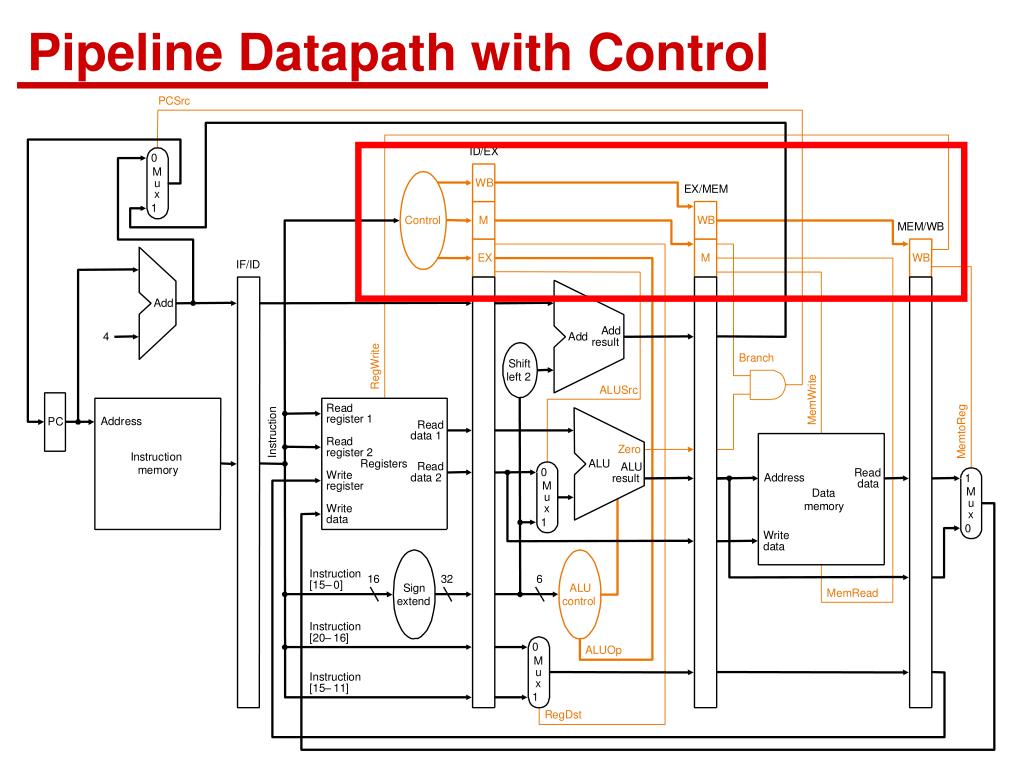

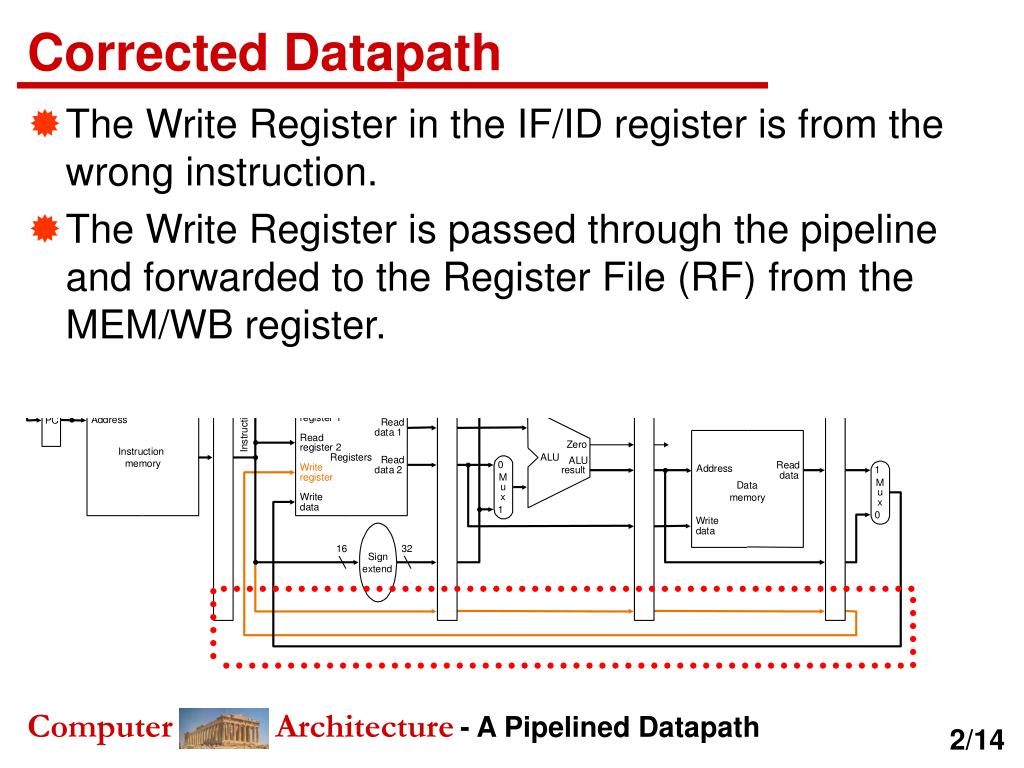

Ppt A Pipelined Datapath Powerpoint Presentation Free Download Id About pipeline speedup if all stages are balanced, i.e. all take the same time time between instructions (pipelined) = time between instructions (non pipelined) # of stages if not balanced, speedup will be less speedup is due to increased throughput, but instruction latency does not change. Data paths are essential parts of the computer architecture that work in a processor to execute instructions. there are two basic categorized methodologies in datapath design: multi cycle data paths and pipeline data paths. • fig. 7.9.5 shows the single cycle datapath with added control to the pipelined datapath. • this datapath uses the control logic for pc source, register destination number, and alu control discussed in the previous section. In this section, we continue our quest for efficient computation by discovering that we can overlay single cycle datapaths in time to produce a type of computational architecture called pipelining. The document discusses the implementation of a five stage pipelined processor datapath. it consists of five stages instruction fetch (if), instruction decode and register read (id), execute (ex), memory access (mem), and write back (wb). — a single cycle datapath executes each instruction in just one clock cycle, but the cycle time may be very long. — a multicycle datapath has much shorter cycle times, but each instruction requires many cycles to execute. pipelining gives the best of both worlds and is used in just about every modern processor.

Ppt A Pipelined Datapath Powerpoint Presentation Free Download Id • fig. 7.9.5 shows the single cycle datapath with added control to the pipelined datapath. • this datapath uses the control logic for pc source, register destination number, and alu control discussed in the previous section. In this section, we continue our quest for efficient computation by discovering that we can overlay single cycle datapaths in time to produce a type of computational architecture called pipelining. The document discusses the implementation of a five stage pipelined processor datapath. it consists of five stages instruction fetch (if), instruction decode and register read (id), execute (ex), memory access (mem), and write back (wb). — a single cycle datapath executes each instruction in just one clock cycle, but the cycle time may be very long. — a multicycle datapath has much shorter cycle times, but each instruction requires many cycles to execute. pipelining gives the best of both worlds and is used in just about every modern processor.

Ppt Pipelined Datapath And Control Powerpoint Presentation Free The document discusses the implementation of a five stage pipelined processor datapath. it consists of five stages instruction fetch (if), instruction decode and register read (id), execute (ex), memory access (mem), and write back (wb). — a single cycle datapath executes each instruction in just one clock cycle, but the cycle time may be very long. — a multicycle datapath has much shorter cycle times, but each instruction requires many cycles to execute. pipelining gives the best of both worlds and is used in just about every modern processor.

Comments are closed.