L04_b Risc V Single Cycle Implementation Part 1

Github M1nhk Risc V Single Cycle Enjoy the videos and music you love, upload original content, and share it all with friends, family, and the world on . Microprocessor system and interfacing class l04 b risc v single cycle implementation.pdf.

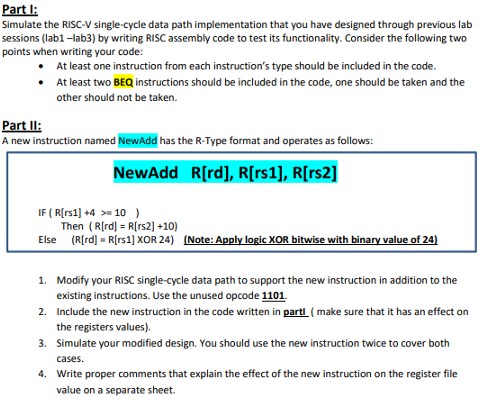

Solved Part 1 Simulate The Risc V Single Cycle Data Path Chegg Slides for general risc isa implementation are adapted from lecture slides for “computer organization and design, risc v edition: the hardware software interface” textbook for general risc isa implementation. This repo contains course materials including lecture slides, lecture videos, assignments, and end of semester projects computer architecture and microprocessor system class l04 b risc v single cycle implementation.pdf at main · dennisgookyi computer architecture and microprocessor system class. Abstract: this research paper presents the design and implementation of a 32 bit single cycle risc v (rv32i) processor using verilog hdl, targeting fpga based deployment for educational and embedded system applications. In this playlist, we explore the design and implementation of a risc v single cycle processor core using verilog. designed for both beginners and experienced.

Github Mohamedhussein27 Risc V Single Cycle Implementation This Abstract: this research paper presents the design and implementation of a 32 bit single cycle risc v (rv32i) processor using verilog hdl, targeting fpga based deployment for educational and embedded system applications. In this playlist, we explore the design and implementation of a risc v single cycle processor core using verilog. designed for both beginners and experienced. Read instruction at pc in memory (stored as 32 bits) from those 32 bits, outputs signals to control the processor to execute the instruction. common exam question: implement part of the decoder with logic gates. Control is the sequential logic that reconfigures the datapath to allow the “data” to flow properly through the hardware components. This document discusses the design of a risc v single cycle datapath, emphasizing the importance of understanding the instruction set architecture (isa) before diving into processor organization. Understanding risc and the single cycle datapath is just the beginning. for deeper insights, explore concepts like pipelining, multi cycle datapaths, and out of order execution.

Github Mkrekker Single Cycle Risc V Read instruction at pc in memory (stored as 32 bits) from those 32 bits, outputs signals to control the processor to execute the instruction. common exam question: implement part of the decoder with logic gates. Control is the sequential logic that reconfigures the datapath to allow the “data” to flow properly through the hardware components. This document discusses the design of a risc v single cycle datapath, emphasizing the importance of understanding the instruction set architecture (isa) before diving into processor organization. Understanding risc and the single cycle datapath is just the beginning. for deeper insights, explore concepts like pipelining, multi cycle datapaths, and out of order execution.

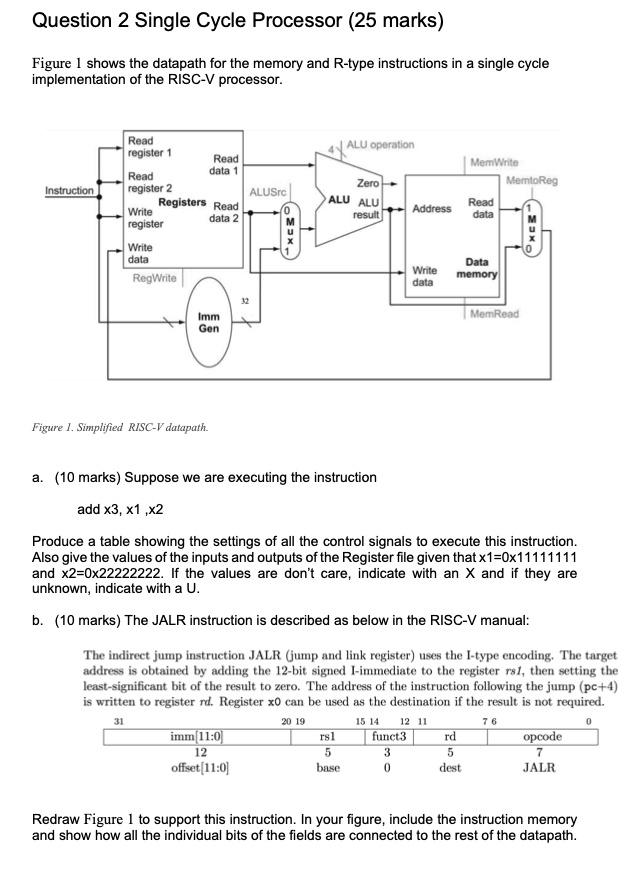

Question 2 Single Cycle Processor25 Marks Figure 1 Shows The Datapath This document discusses the design of a risc v single cycle datapath, emphasizing the importance of understanding the instruction set architecture (isa) before diving into processor organization. Understanding risc and the single cycle datapath is just the beginning. for deeper insights, explore concepts like pipelining, multi cycle datapaths, and out of order execution.

Comments are closed.