Introducing Asynchronous Srams With Error Correcting Code Ecc

4 Mb Asynchronous Srams With On Chip Error Correcting Code Circuit Cellar Y read incorrect data. to mitigate this problem, cypress’s latest generation asynchronous sram devices include an optional erro. indication (err) pin. during read operation, the err pin signals detection and correction of a single bit error at the ac. This industry’s first error correcion code (ecc) based asynchronous sram meets high quality requirements in automotive, industrial, military aerospace, and other applications.

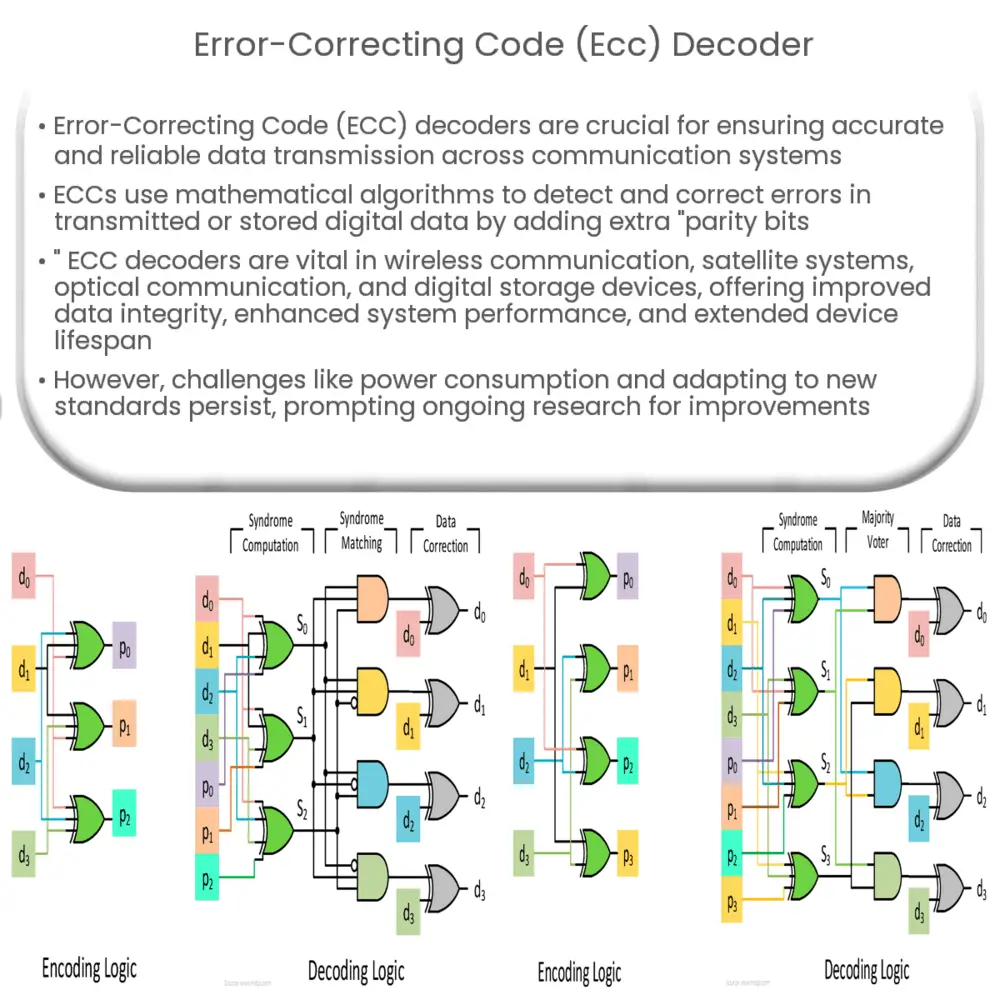

Error Correcting Code Ecc Decoder How It Works Application The ecc sram core adds protection against sram data corruption. it uses error correcting code (ecc) to implement single bit error correction and double bit error detection (secdec). A hardware ecc block in cypress's new asynchronous srams performs all error correction functions inline, without user intervention, delivering best in class soft error rate (ser). The new rad hard srams are available in eight , 16 and 32 bit wide configurations and offer embedded error correction code (ecc) for single bit error correction. The ecc sram core adds protection against sram data corruption. it uses error correcting code (ecc) to implement single bit error correction and double bit error detection (secdec).

Rad Hard Asynchronous Srams Have Embedded Ecc Softei Global The new rad hard srams are available in eight , 16 and 32 bit wide configurations and offer embedded error correction code (ecc) for single bit error correction. The ecc sram core adds protection against sram data corruption. it uses error correcting code (ecc) to implement single bit error correction and double bit error detection (secdec). A hardware ecc block in cypress’s new ssynchronous srams performs all error correction functions inline, without user intervention, delivering lowest soft error rate (ser) performance. Cypress’s latest generation asynchronous sram devices use (38,32) hamming code for single bit error detection and correction using ecc. the hardware ecc block in cypress’ ultra reliable asynchronous srams performs all ecc related functions in line, without user intervention. This application note is intended to describe how the ecc protection is implemented in s32k1xx family and understand the particular ecc event response for s32k14x and s32k11x devices. it also offers some software examples for illustration of mentioned behavior. We have also implemented an error correcting code (ecc) subsystem on another block of the sram, this is capable of both detecting and correcting a single bit error in each long word of sram and detecting a 2 bit error. this greatly increases the reliability of data held in the ecc sram.

Mobl Ultra Reliable Asynchronous Srams Infineon Technologies Mouser A hardware ecc block in cypress’s new ssynchronous srams performs all error correction functions inline, without user intervention, delivering lowest soft error rate (ser) performance. Cypress’s latest generation asynchronous sram devices use (38,32) hamming code for single bit error detection and correction using ecc. the hardware ecc block in cypress’ ultra reliable asynchronous srams performs all ecc related functions in line, without user intervention. This application note is intended to describe how the ecc protection is implemented in s32k1xx family and understand the particular ecc event response for s32k14x and s32k11x devices. it also offers some software examples for illustration of mentioned behavior. We have also implemented an error correcting code (ecc) subsystem on another block of the sram, this is capable of both detecting and correcting a single bit error in each long word of sram and detecting a 2 bit error. this greatly increases the reliability of data held in the ecc sram.

Comments are closed.