Improving Verification Methodologies Ann Mutschler

Improving Verification Methodologies Ann Mutschler Verification tools are getting faster and capacity is increasing, but they still can’t keep up with the problem space. verification is crossing more silos, requiring expanded skill sets. At the conference, we learned about new developments in specman, advanced tool capabilities, methodologies for bug research and more efficient rtl verification r&d, as well as hardware security.

Improving Verification Validation In The Medical D Pdf Verification This paper explores the integration of artificial intelligence (ai) with universal verification methodology (uvm) to enhance the efficiency and effectiveness of the verification process. Continuous design innovation adds to verification complexity, and pushes more companies to actually do it. Key takeaways ai will enhance, not replace, verification ip by automating test generation and debug. verification ip’s core value will increasingly lie in trust, accountability, and system level realism, especially as designs become more complex, multi die, and security sensitive. Agile development is gaining traction for developing hardware testbenches, but challenges remain. december 26th, 2018 – by: ann steffora mutschler agile methodologies, created to improve quality in software code, increasingly are being applied to hardware verification.

Elizabeth Mutschler Obituary 1941 2023 Ann Arbor Mi Ann Arbor News Key takeaways ai will enhance, not replace, verification ip by automating test generation and debug. verification ip’s core value will increasingly lie in trust, accountability, and system level realism, especially as designs become more complex, multi die, and security sensitive. Agile development is gaining traction for developing hardware testbenches, but challenges remain. december 26th, 2018 – by: ann steffora mutschler agile methodologies, created to improve quality in software code, increasingly are being applied to hardware verification. The verification problem space is outpacing the speed of the tools, placing an increasing burden on verification methodologies and automation improvements. by brian bailey at semiconductor. Verification tools are getting faster and capacity is increasing, but they still can’t keep up with the problem space. verification is crossing more silos, requiring expanded skill sets. Frank schirrmeister, senior group director for product management and marketing at cadence, discusses how to verify different use cases, focusing on software, low power designs, connectivity, and a variety of end markets. Today, the predominant bug finding approaches use the ubiquitous constrained random coverage driven verification technology, or formal verification technology. but as designs become more complex, new methodologies and approaches need to be applied to ensure quality over time.

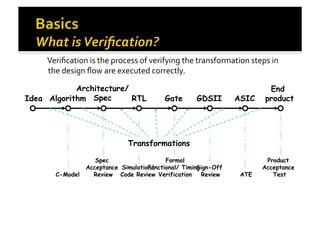

Verification Challenges And Methodologies Pdf The verification problem space is outpacing the speed of the tools, placing an increasing burden on verification methodologies and automation improvements. by brian bailey at semiconductor. Verification tools are getting faster and capacity is increasing, but they still can’t keep up with the problem space. verification is crossing more silos, requiring expanded skill sets. Frank schirrmeister, senior group director for product management and marketing at cadence, discusses how to verify different use cases, focusing on software, low power designs, connectivity, and a variety of end markets. Today, the predominant bug finding approaches use the ubiquitous constrained random coverage driven verification technology, or formal verification technology. but as designs become more complex, new methodologies and approaches need to be applied to ensure quality over time.

Comments are closed.