Github Rufaida Kassem Spi Implementation

Github Rufaida Kassem Spi Implementation Contribute to rufaida kassem spi implementation development by creating an account on github. This article is a continuation of the series on linux device drivers and carries the discussion on linux device drivers and their implementation. the aim of this series is to provide easy and practical examples that anyone can understand.

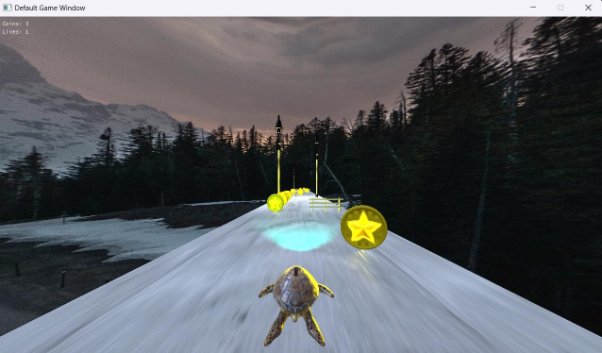

Github Rufaida Kassem Wild Run Contribute to rufaida kassem spi implementation development by creating an account on github. Contribute to rufaida kassem spi implementation development by creating an account on github. Contribute to rufaida kassem spi implementation development by creating an account on github. 🚀 project completed – spi slave with single port ram 🎯 i’m excited to share that our team lut on town has successfully completed the design, verification, and optimization of an spi.

Github Rufaida Kassem Wild Run Contribute to rufaida kassem spi implementation development by creating an account on github. 🚀 project completed – spi slave with single port ram 🎯 i’m excited to share that our team lut on town has successfully completed the design, verification, and optimization of an spi. Full chip implementation of the picorv32 picosoc in x fab xh018. the raven chip contains two adcs, a dac, comparator, bandgap, rc oscillator, and over temperature alarm, as well as 16 bits of general purpose digital inputs outputs. This video walks through the spi master implementation for verilog in an fpga. check my video on the basics of spi if you're unfamiliar with how this interface works. Welcome back to installment two of our series on how to implement spi communication protocol on asic. now before we dive in, you must have some basic working knowledge about boolean operators. Still on the to do list are ddr2 and lpddr2 support, can, spi, and i2c buses, and ethernet support, among other features. fuse zynq is available on craig's github repository under an unspecified open source licence.

Github Artaasadi Spi Implementation Implemented Spi Transfer Full chip implementation of the picorv32 picosoc in x fab xh018. the raven chip contains two adcs, a dac, comparator, bandgap, rc oscillator, and over temperature alarm, as well as 16 bits of general purpose digital inputs outputs. This video walks through the spi master implementation for verilog in an fpga. check my video on the basics of spi if you're unfamiliar with how this interface works. Welcome back to installment two of our series on how to implement spi communication protocol on asic. now before we dive in, you must have some basic working knowledge about boolean operators. Still on the to do list are ddr2 and lpddr2 support, can, spi, and i2c buses, and ethernet support, among other features. fuse zynq is available on craig's github repository under an unspecified open source licence.

Github Rufaida Kassem Alu With Class Based Tb Sv A Verification Welcome back to installment two of our series on how to implement spi communication protocol on asic. now before we dive in, you must have some basic working knowledge about boolean operators. Still on the to do list are ddr2 and lpddr2 support, can, spi, and i2c buses, and ethernet support, among other features. fuse zynq is available on craig's github repository under an unspecified open source licence.

Github Fangyzh26 Spi

Comments are closed.