Github Chrisssssss323 Risc V Using Myth

Github 06bejaia Myth Risc V Cpu Contribute to chrisssssss323 risc v using myth development by creating an account on github. Contribute to chrisssssss323 risc v using myth development by creating an account on github.

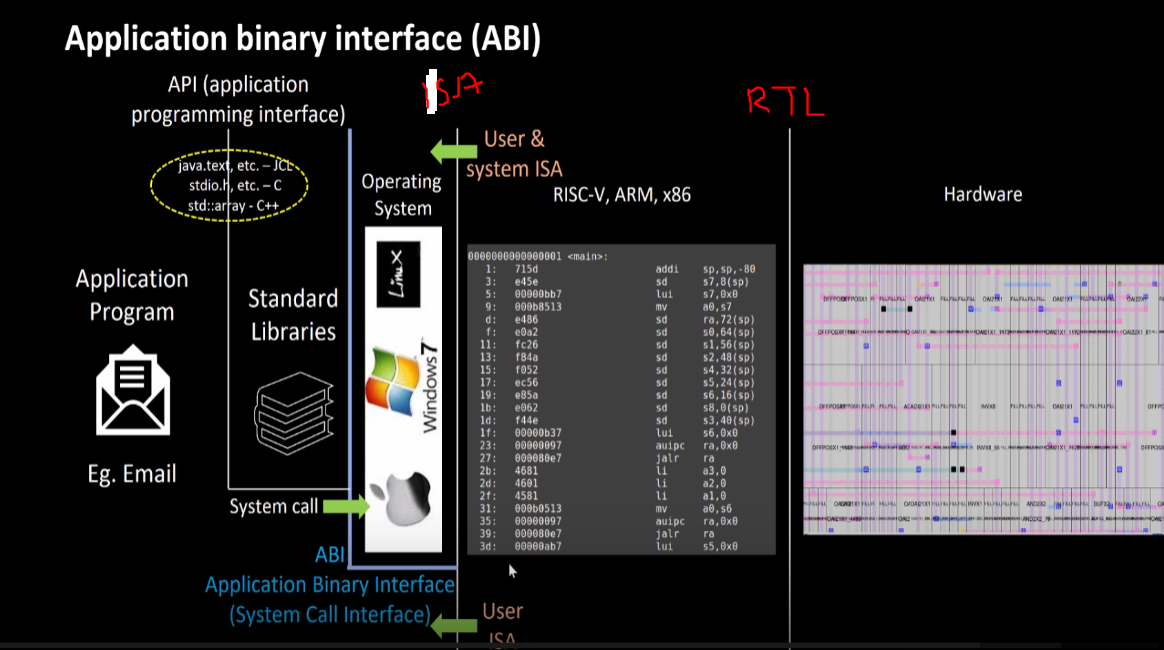

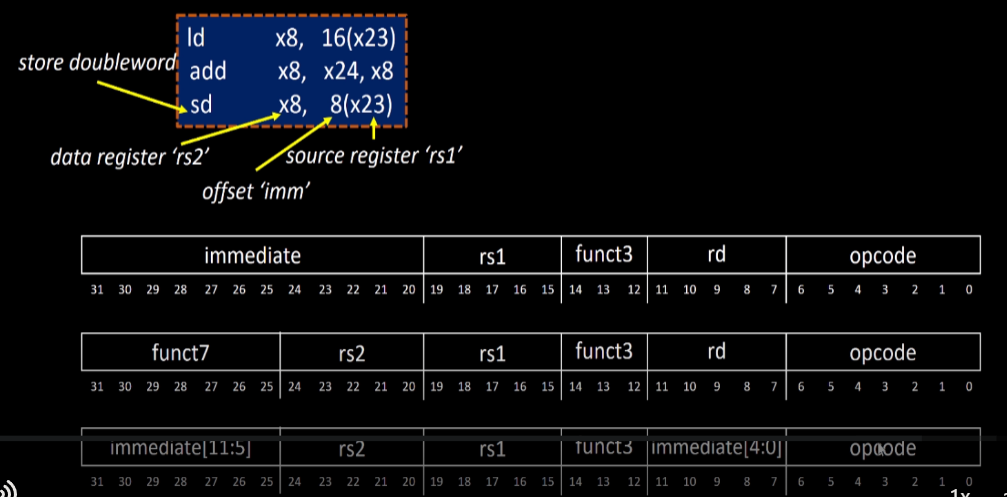

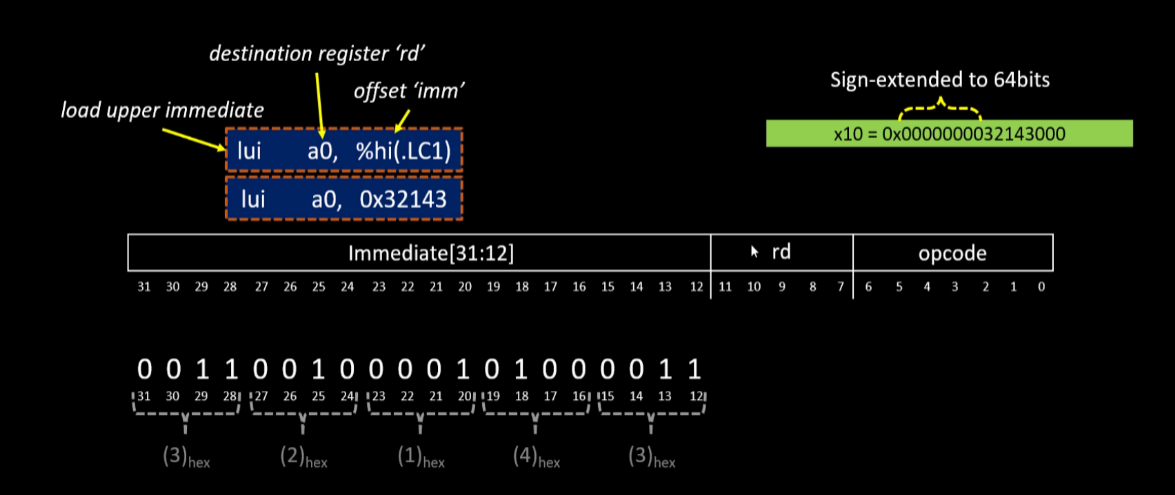

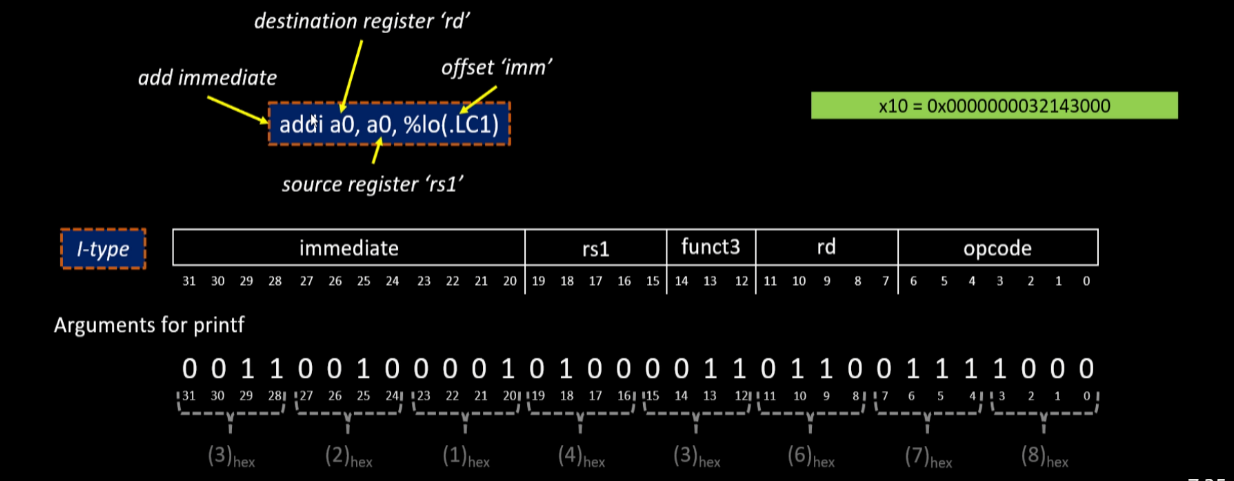

Github Chrisssssss323 Risc V Using Myth The “risc v based myth (microprocessor for you in thirty hours)” workshop introduces participants to risc v architecture, guiding them from software concepts to hardware implementation. Nothing is better than having a playable example that is both small and functional. this repo already contains a risc v processor core implementation that is synthesizable by itself, but also directly works with a minimal emulator (verilator based) code with a realistic system setup. Hello to all, i'm excited to share that i have completed "risc v based myth design project" workshop offered by vsd, redwood eda and nasscom future skills program. the workshop lasted 10 days. Course 1: risc v based myth (microprocessors for you in thirty hours). overview:. a beginner level 5 day workshop on “risc v based myth” (24hrs x 5days on vsd iat platform). when we say, “beginner level”, by end of the workshop you will understand:. 1) risc v specs basics. 2) risc v software basics.

Github Chrisssssss323 Risc V Using Myth Hello to all, i'm excited to share that i have completed "risc v based myth design project" workshop offered by vsd, redwood eda and nasscom future skills program. the workshop lasted 10 days. Course 1: risc v based myth (microprocessors for you in thirty hours). overview:. a beginner level 5 day workshop on “risc v based myth” (24hrs x 5days on vsd iat platform). when we say, “beginner level”, by end of the workshop you will understand:. 1) risc v specs basics. 2) risc v software basics. Setting up risc v github actions runners to build and publish riscv64 docker images of nanoclaw automatically. part 2 of a 2 part series covering feas. tagged with riscv, riscv64, nanoclaw, githubactions. Risc v (pronounced "risk five") [3]: 1 is a free and open standard instruction set architecture (isa) based on reduced instruction set computer (risc) principles. unlike proprietary isas such as x86 and arm, risc v is described as "free and open" because its specifications are released under permissive open source licenses and can be implemented without paying royalties. [4] risc v was. Below is a detailed step by step guide to help you replicate this on your risc v system, along with warnings about the challenges and tips for using ai to troubleshoot errors. Nexcess theeeview nexcess.

Github Chrisssssss323 Risc V Using Myth Setting up risc v github actions runners to build and publish riscv64 docker images of nanoclaw automatically. part 2 of a 2 part series covering feas. tagged with riscv, riscv64, nanoclaw, githubactions. Risc v (pronounced "risk five") [3]: 1 is a free and open standard instruction set architecture (isa) based on reduced instruction set computer (risc) principles. unlike proprietary isas such as x86 and arm, risc v is described as "free and open" because its specifications are released under permissive open source licenses and can be implemented without paying royalties. [4] risc v was. Below is a detailed step by step guide to help you replicate this on your risc v system, along with warnings about the challenges and tips for using ai to troubleshoot errors. Nexcess theeeview nexcess.

Github Chrisssssss323 Risc V Using Myth Below is a detailed step by step guide to help you replicate this on your risc v system, along with warnings about the challenges and tips for using ai to troubleshoot errors. Nexcess theeeview nexcess.

Github Chrisssssss323 Risc V Using Myth

Comments are closed.