Fpga Prototyping Think

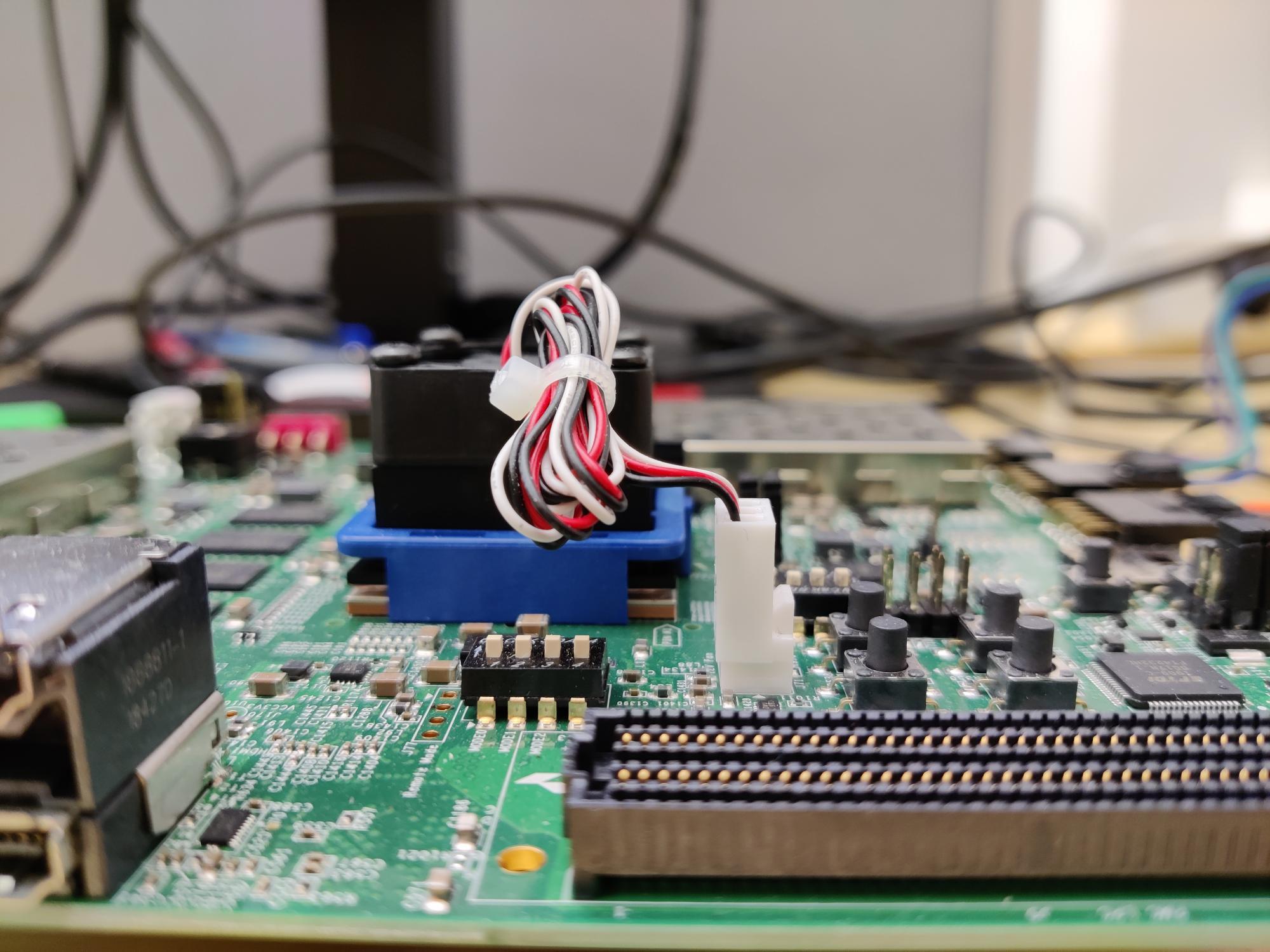

Fpga Front Runners Prototyping Systems Using Fpga Desn We leverage the power of field programmable gate array (fpga) technology, along with advanced simulation and synthesis tools, to deliver innovative solutions for the rapid development of highly integrated digital systems. So, in a nutshell, the fpga based prototype system is a pre silicon digital twin of your soc or ip design. this digital twin is now a cycle accurate representation of your design, running fast enough to boot the firmware and the operating system and to run the actual software workloads.

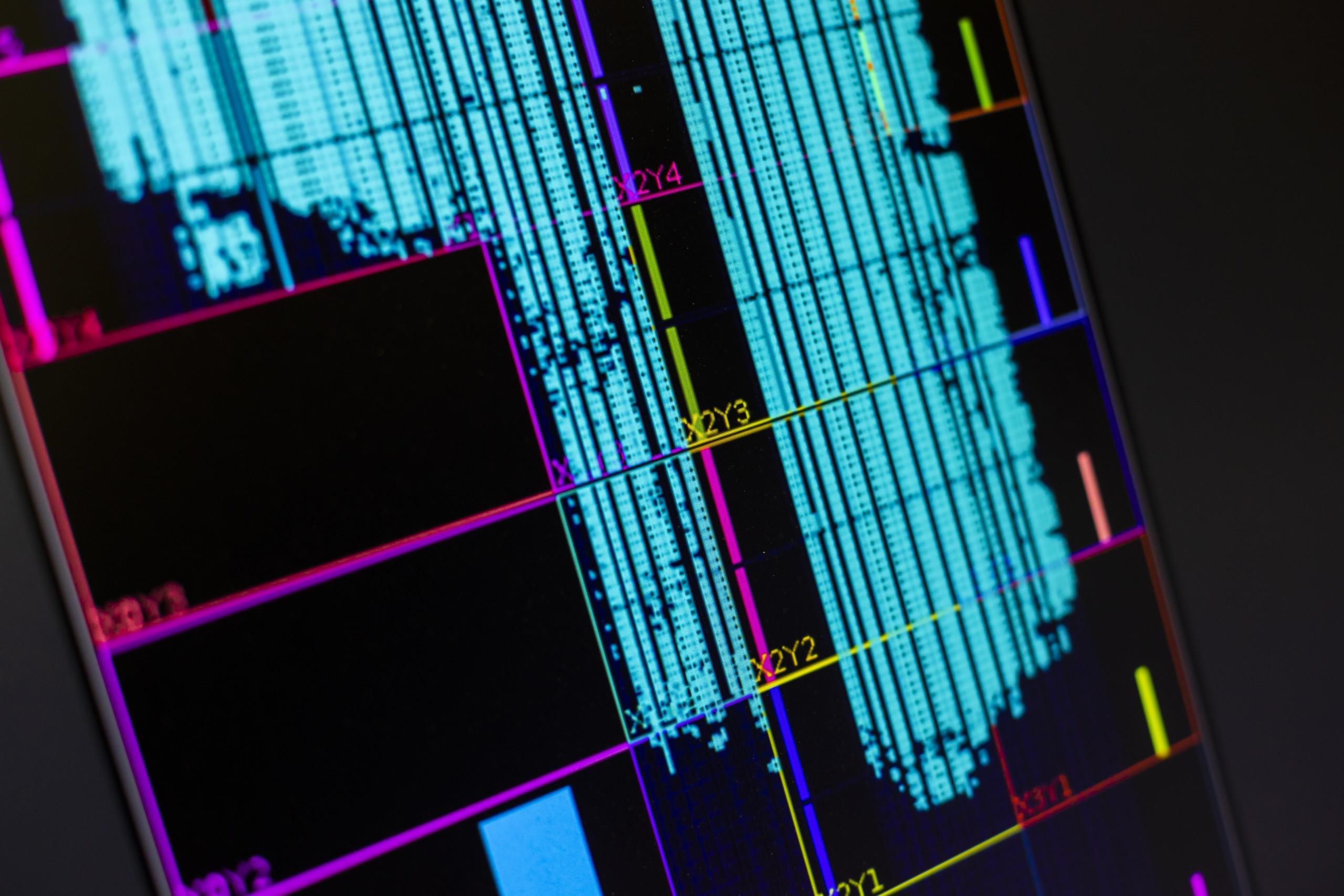

Fpga Prototyping Think And i couldn’t even have envisaged something like fpga based prototyping and verification. one reason for this, of course, is that fpgas didn’t even exist at that time. The fpga based prototyping methodology manual: best practices in design for prototyping (fpmm) is a comprehensive and practical guide to using fpgas as a platform for soc development and verification. Abstract: this article presents guidelines for using fpgas to prototype asic or soc designs quickly. it covers partitioning strategies, clock domain synchronization, and resource optimization to minimize timing issues. Learn the role of fpga in prototyping and system development, including design validation, risk reduction, and faster iteration before asic production.

Fpga Prototyping Signoff Semiconductors Abstract: this article presents guidelines for using fpgas to prototype asic or soc designs quickly. it covers partitioning strategies, clock domain synchronization, and resource optimization to minimize timing issues. Learn the role of fpga in prototyping and system development, including design validation, risk reduction, and faster iteration before asic production. Welcome to our comprehensive guide on fpga based prototyping. in this article, we will dive into the world of fpga accelerated prototyping, design verification, development boards, rapid prototyping, implementation tools, prototyping platforms, emulation, and the wide range of solutions available. We will explore the realm of fpga based prototyping and its importance in contemporary engineering in this blog article. we’ll go into fpgas’ underlying technology, their benefits over conventional prototype techniques, and their uses in a variety of industries. Below are the key steps of fpga prototyping, including design partitioning, post partition system level timing analysis, programing and downloading, as well as functional verification and debug. Running an soc design on an fpga prototype is a reliable way to ensure that it is functionally correct. about a third of all current soc designs are fault free during their first silicon pass, with nearly half of all re spins caused by functional logic errors.

What Is Fpga Prototyping Soc Hub Welcome to our comprehensive guide on fpga based prototyping. in this article, we will dive into the world of fpga accelerated prototyping, design verification, development boards, rapid prototyping, implementation tools, prototyping platforms, emulation, and the wide range of solutions available. We will explore the realm of fpga based prototyping and its importance in contemporary engineering in this blog article. we’ll go into fpgas’ underlying technology, their benefits over conventional prototype techniques, and their uses in a variety of industries. Below are the key steps of fpga prototyping, including design partitioning, post partition system level timing analysis, programing and downloading, as well as functional verification and debug. Running an soc design on an fpga prototype is a reliable way to ensure that it is functionally correct. about a third of all current soc designs are fault free during their first silicon pass, with nearly half of all re spins caused by functional logic errors.

What Is Fpga Prototyping Soc Hub Below are the key steps of fpga prototyping, including design partitioning, post partition system level timing analysis, programing and downloading, as well as functional verification and debug. Running an soc design on an fpga prototype is a reliable way to ensure that it is functionally correct. about a third of all current soc designs are fault free during their first silicon pass, with nearly half of all re spins caused by functional logic errors.

Comments are closed.