Fpga 21 How To Do Verilog Parameterization

Github Sgurkirpal Fpga Verilog A hands on tutorial on how to do parameterization with verilog. #fpga #verilog #simulation #logic more. Learn how to create reusable verilog a models using parameters, modular structure, scalable equations, and best practices that improve flexibility, portability, and maintainability in analog behavioral modeling.

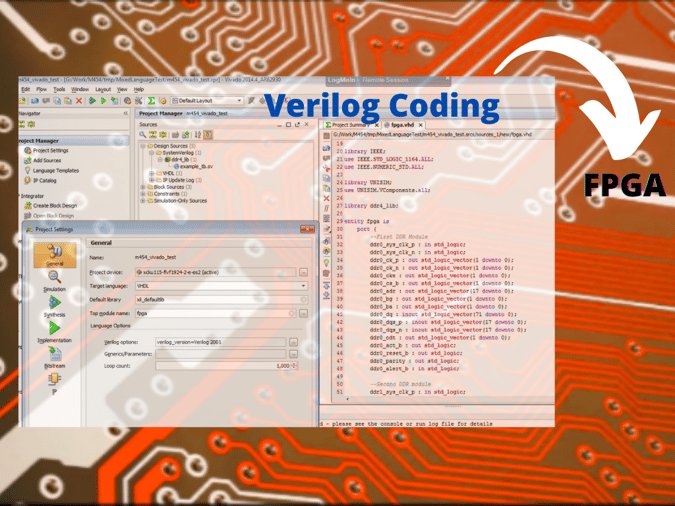

Github Emrealci Fpga Verilog Practices Related To The Fundamental Parameters are verilog constructs that allow a module to be reused with a different specification. for example, a 4 bit adder can be parameterized to accept a value for the number of bits and new parameter values can be passed in during module instantiation. Understand how to apply parameterization and delays in verilog to design flexible, reusable digital systems. Download the coding example files from coding examples . a verilog parameter allows to control the width of an instantitated. block describing register logic. file:parameter 1.v. module myreg (clk, clken, d, q); parameter size = 1; input clk, clken; input [size 1:0] d; output reg [size 1:0] q;. Learn how to use verilog parameters for flexible and reusable designs with examples on module, local, and specify parameters.

Fpga Verilog Programming Skillsuniverse Technologies Download the coding example files from coding examples . a verilog parameter allows to control the width of an instantitated. block describing register logic. file:parameter 1.v. module myreg (clk, clken, d, q); parameter size = 1; input clk, clken; input [size 1:0] d; output reg [size 1:0] q;. Learn how to use verilog parameters for flexible and reusable designs with examples on module, local, and specify parameters. Verilog, as one of the most widely used hardware description languages (hdls), plays a critical role in designing and verifying digital systems such as fpgas and asics. Discover how we expertly utilize the 'parameter in verilog' for efficient hardware design and modular coding in our in depth guide. Nobody's responded to this post yet. add your thoughts and get the conversation going. All inputs are constant, so the output is also constant the result can be computed at elaboration, so there is no reason to build hardware to do it constant functions are useful when one constant value is dependent on another. it can simplify the calculation of values in parameterized modules.

Verilog Fpga Design 6 Days Comprehensive Course Verilog, as one of the most widely used hardware description languages (hdls), plays a critical role in designing and verifying digital systems such as fpgas and asics. Discover how we expertly utilize the 'parameter in verilog' for efficient hardware design and modular coding in our in depth guide. Nobody's responded to this post yet. add your thoughts and get the conversation going. All inputs are constant, so the output is also constant the result can be computed at elaboration, so there is no reason to build hardware to do it constant functions are useful when one constant value is dependent on another. it can simplify the calculation of values in parameterized modules.

Comments are closed.