Foundation Logic Synthesis

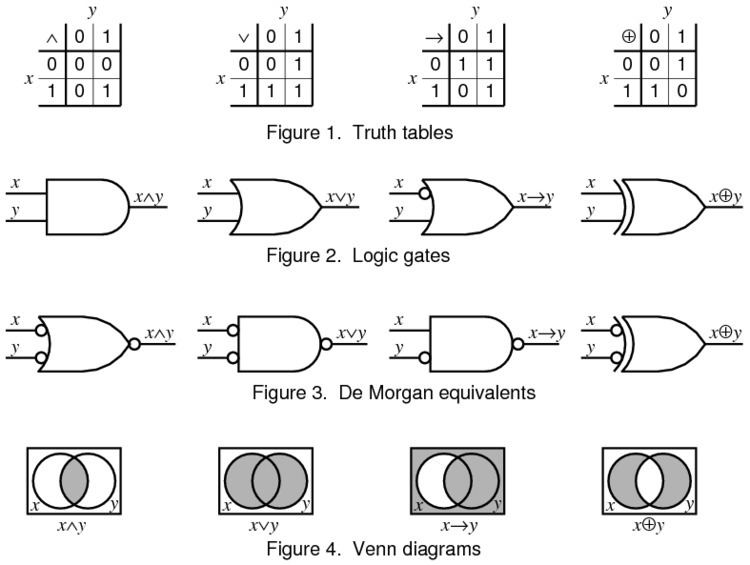

Synthesis Pdf Logic Synthesis Hardware Description Language Welcome to the course logic synthesis your journey to learning the concepts of logic synthesis. the course gives a holistic approach to learning the concepts through a demo. The main mathematical foundation of logic synthesis is the intersection of logic and algebra. the \algebra of logic" created by george boole in 1847, a.k.a. boolean algebra, is at the core of logic synthesis.

Bundle Of Logic Synthesis Physical Design And Sta With this foundation, you're ready to perform actual synthesis using yosys, exploring hands on how rtl transforms into gates and learning to optimize designs for real world constraints. The main mathematical foundation of logic synthesis is the intersection of logic and algebra. the “algebra of logic” created by george boole in 1847, a.k. a. boolean algebra, is at the core of logic synthesis. This process involves translating the behavioral or structural description of the circuit into a network of logic gates. in this chapter, we will focus on the core algorithms used in logic synthesis, examining their approaches, advantages, and limitations. The main mathematical foundation of logic synthesis is the intersection of logic and algebra. the \algebra of logic" created by george boole in 1847, a.k.a. boolean algebra, is at the core of logic synthesis.

Lecture 3 Synthesis Part 1 Pdf Logic Synthesis Library Computing This process involves translating the behavioral or structural description of the circuit into a network of logic gates. in this chapter, we will focus on the core algorithms used in logic synthesis, examining their approaches, advantages, and limitations. The main mathematical foundation of logic synthesis is the intersection of logic and algebra. the \algebra of logic" created by george boole in 1847, a.k.a. boolean algebra, is at the core of logic synthesis. .logic synthesis programs transform boolean expressions or register transfer level (rtl) description (in verilog vhdl c) into logic gate networks (netlist) in a particular library. This write up is intended to get you started with the foundation tools. it gives a quick overview of how to create a design, simulate it and download it into a fpga or cpld. Both bdd and sat solving have had a major impact on the way logic expressions are represented and analyzed, which is at the very basis of efficient logic synthesis methods. The synthesis outputs, including the netlist, updated upf, and def files, provide a detailed and optimized foundation for subsequent design phases. the netlist describes the gate level circuit, the updated upf reflects accurate power intent, and def files outline the precise cell and macro placements.

Logic Synthesis Flow Rtl Synthesis Flow Rtl2gds Design 60 Off .logic synthesis programs transform boolean expressions or register transfer level (rtl) description (in verilog vhdl c) into logic gate networks (netlist) in a particular library. This write up is intended to get you started with the foundation tools. it gives a quick overview of how to create a design, simulate it and download it into a fpga or cpld. Both bdd and sat solving have had a major impact on the way logic expressions are represented and analyzed, which is at the very basis of efficient logic synthesis methods. The synthesis outputs, including the netlist, updated upf, and def files, provide a detailed and optimized foundation for subsequent design phases. the netlist describes the gate level circuit, the updated upf reflects accurate power intent, and def files outline the precise cell and macro placements.

Logic Synthesis Alchetron The Free Social Encyclopedia Both bdd and sat solving have had a major impact on the way logic expressions are represented and analyzed, which is at the very basis of efficient logic synthesis methods. The synthesis outputs, including the netlist, updated upf, and def files, provide a detailed and optimized foundation for subsequent design phases. the netlist describes the gate level circuit, the updated upf reflects accurate power intent, and def files outline the precise cell and macro placements.

Comments are closed.