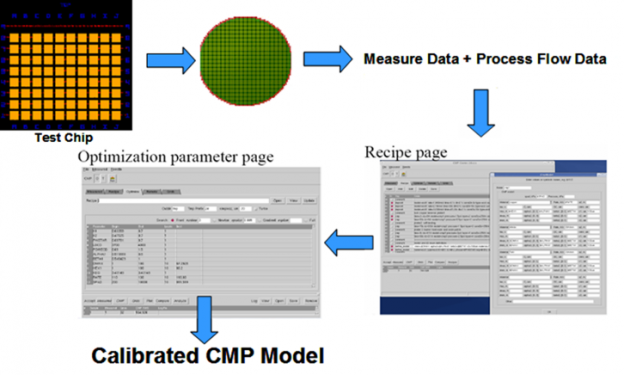

Fig2 Cmp Model Flow Semiconductor Digest

Fig2 Cmp Model Flow Semiconductor Digest Fig2 cmp model flow published october 19, 2017 at 726 × 436 in fig2 cmp model flow. ← previous next →. We present a modeling and hotspot detection solution for the eoe phenomenon. chemical mechanical polishing planarization (cmp) is a key technology for achieving surface planarity during the manufacturing of multi level interconnections of semiconductor chips and electronic devices.

Cmp In Semiconductor Manufacturing Pdf Semiconductor Device Cmp modeling has become a powerful tool for both process engineers and chip designers. it enables design teams to detect potential cmp hotspots prior to manufacturing by providing visualization and analysis of simulated cmp results. A general methodology for cmp model application in assisting integrated circuit design and manufacturing is presented. finally, future needs and challenges for cmp modeling are discussed, particularly to address advanced or alternative cmp consumable properties. This paper reviews cmp fill techniques as a dfm process, then describes a power aware methodology wherein cmp fill synthesis is integrated within a holistic design and manufacturing driven flow. Chemical mechanical planarization (cmp) was introduced into semiconductor manufacturing in the 1980’s as a way to reduce uneven topography on the wafer. the process has been adopted by virtually all semiconductor fabrication facilities producing feature sizes below 0.35 micron.

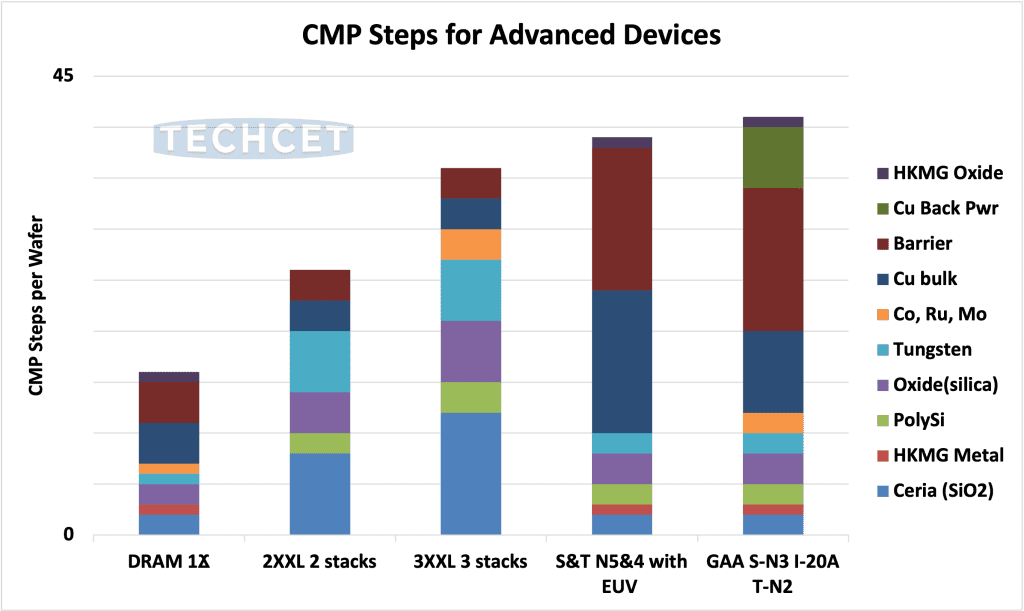

Semiconductor Cmp Pad Slurry Forecast Semiconductor Digest This paper reviews cmp fill techniques as a dfm process, then describes a power aware methodology wherein cmp fill synthesis is integrated within a holistic design and manufacturing driven flow. Chemical mechanical planarization (cmp) was introduced into semiconductor manufacturing in the 1980’s as a way to reduce uneven topography on the wafer. the process has been adopted by virtually all semiconductor fabrication facilities producing feature sizes below 0.35 micron. Explore advanced cmp process simulation and modeling in semiconductor manufacturing with data analytics and bi insights. As, modeling of the post ecd surface profile is critical to ensuring high accuracy cmp modeling. non planar surface profiles are also typical for feol layers. Written by researchers at uc berkeley, this monograph reviews cmp modeling literature (from preston to present day efforts) and develops, with a strong emphasis on mechanical elements of cmp, an integrated model of cmp addressing wafer,die and particle scale mechanisms and features. Chemical mechanical polishing (cmp) is a key process in integrated circuit (ic) manufacturing, used to ensure surface planarity. successful fabrication and performance of semiconductor devices is highly dependent on the final planarity of the processed layers.

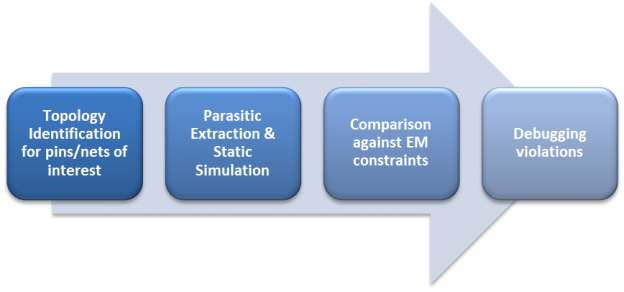

Fig3 Analysis Flow Semiconductor Digest Explore advanced cmp process simulation and modeling in semiconductor manufacturing with data analytics and bi insights. As, modeling of the post ecd surface profile is critical to ensuring high accuracy cmp modeling. non planar surface profiles are also typical for feol layers. Written by researchers at uc berkeley, this monograph reviews cmp modeling literature (from preston to present day efforts) and develops, with a strong emphasis on mechanical elements of cmp, an integrated model of cmp addressing wafer,die and particle scale mechanisms and features. Chemical mechanical polishing (cmp) is a key process in integrated circuit (ic) manufacturing, used to ensure surface planarity. successful fabrication and performance of semiconductor devices is highly dependent on the final planarity of the processed layers.

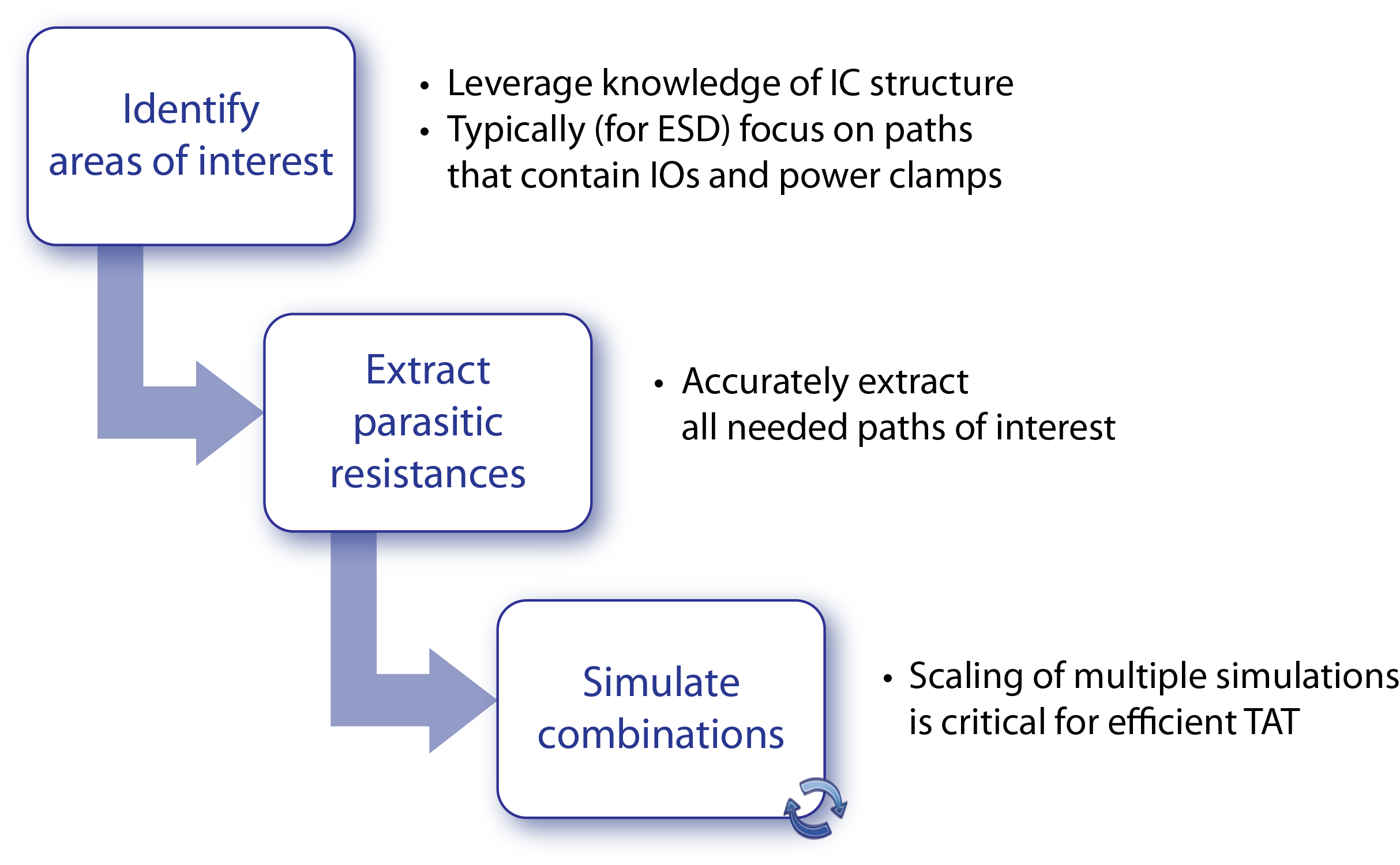

Fig2 Perc Flow Semiconductor Digest Written by researchers at uc berkeley, this monograph reviews cmp modeling literature (from preston to present day efforts) and develops, with a strong emphasis on mechanical elements of cmp, an integrated model of cmp addressing wafer,die and particle scale mechanisms and features. Chemical mechanical polishing (cmp) is a key process in integrated circuit (ic) manufacturing, used to ensure surface planarity. successful fabrication and performance of semiconductor devices is highly dependent on the final planarity of the processed layers.

Comments are closed.