Device Isolation Techniques Junction And Oxide Isolation

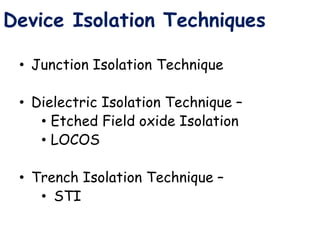

Vlsi Device Isolation Techniques Pdf Solid State Chemistry It systematically covers major isolation techniques including junction isolation, dielectric isolation (etched field oxide and locos), and trench isolation (sti), highlighting their working principles, process steps, and advantages and limitations such as the bird’s beak problem in locos. Vlsi device isolation techniques free download as powerpoint presentation (.ppt .pptx), pdf file (.pdf), text file (.txt) or view presentation slides online. this presentation discusses the various device isolation techniques, while fabricating a chip using vlsi technology.

Device Isolation Techniques Pptx Device isolation techniques in vlsi for the isolation of neighboring mos transistors there exist two techniques, namely local oxidation of silicon (locos) and shallow trench isolation (sti). Schematic representation of the shallow and deep trench structures for inter device and inter well isolation respectively. after etching and re oxidizing the trench sidewalls, they are filled with a deposited dielectric and planarized. Ple isolation techniques such as locos result in oxide encroachment. higher implant dose to aintain the field threshold results in higher diffusion capacitance. the use of thicker field oxide to reduce interconnect capacitance may result in more oxide encroach. Device isolation there are two common approaches to device isolation locos – local oxidation of silicon popular in the 1970s and 1980s sti – shallow trench isolation came in to use in the 1990s preferred method for 250 nm technologies and below.

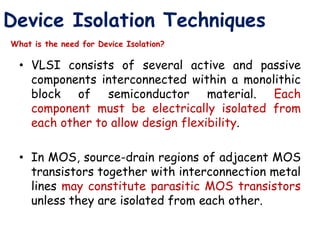

Device Isolation Techniques Pptx Ple isolation techniques such as locos result in oxide encroachment. higher implant dose to aintain the field threshold results in higher diffusion capacitance. the use of thicker field oxide to reduce interconnect capacitance may result in more oxide encroach. Device isolation there are two common approaches to device isolation locos – local oxidation of silicon popular in the 1970s and 1980s sti – shallow trench isolation came in to use in the 1990s preferred method for 250 nm technologies and below. For this purpose, special fabrication processes, which are known as isolation techniques, have been developed and are judged by their ability to minimize the spacing required for electrical isolation of adjacent devices. Oxidation plays a crucial role in vlsi technology, particularly in the formation and isolation of devices on a silicon wafer. the silicon dioxide (sio2) layer formed during oxidation serves multiple purposes, which are essential for creating reliable and functional semiconductor devices. For the isolation of neighboring mos transistors there exist two techniques, namely local oxidation of silicon and shallow trench isolation. the differences in their process flow and their final oxide shapes are described in the following. The document discusses various techniques for electrically isolating devices in integrated circuits. it describes junction isolation, which uses reverse biased pn junctions, but this did not scale well as devices became smaller.

Device Isolation Techniques Pptx For this purpose, special fabrication processes, which are known as isolation techniques, have been developed and are judged by their ability to minimize the spacing required for electrical isolation of adjacent devices. Oxidation plays a crucial role in vlsi technology, particularly in the formation and isolation of devices on a silicon wafer. the silicon dioxide (sio2) layer formed during oxidation serves multiple purposes, which are essential for creating reliable and functional semiconductor devices. For the isolation of neighboring mos transistors there exist two techniques, namely local oxidation of silicon and shallow trench isolation. the differences in their process flow and their final oxide shapes are described in the following. The document discusses various techniques for electrically isolating devices in integrated circuits. it describes junction isolation, which uses reverse biased pn junctions, but this did not scale well as devices became smaller.

Comments are closed.