Developing With Polarfire Soc

Developing For Polar Fire Soc Pptx Polarfire socs combine a deterministic, coherent risc v cpu cluster with an l2 memory subsystem for real time and linux ® applications. explore comprehensive documentation, reference designs and development tools on github to kick start your development journey. To help users get started using polarfire soc we have created a selection of training playlists. the risc v innovation unleashed training series provides webinars describing different aspects of polarfire soc.

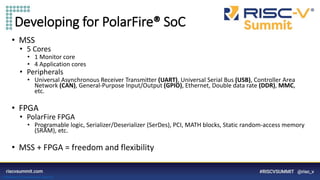

Developing For Polar Fire Soc Pptx To begin working with polarfire soc: this overview provides a foundation for understanding the polarfire soc platform. the following sections will delve deeper into specific aspects of the system architecture, software stack, and development process. With the polarfire ® soc family, microchip has combined a powerful 64 bit 5 core risc v microprocessor sub system (mss) with the polarfire fpga fabric in a single device. packed with this powerful combination, polarfire soc devices offer the scalable features of fpgas and high performance of asics. The document discusses developing applications for the polarfire® system on chip (soc) field programmable gate array (fpga). it notes that developing for the polarfire soc is less complicated than it seems. And this is exactly what we are going to do in this post, start up the microchip polarfire soc and the icicle kit from a blank sheet. the first time that i saw the polarfire soc, with its five risc v core, i thought that it will be difficult to make all of them working.

Developing For Polar Fire Soc Pptx The document discusses developing applications for the polarfire® system on chip (soc) field programmable gate array (fpga). it notes that developing for the polarfire soc is less complicated than it seems. And this is exactly what we are going to do in this post, start up the microchip polarfire soc and the icicle kit from a blank sheet. the first time that i saw the polarfire soc, with its five risc v core, i thought that it will be difficult to make all of them working. It has the base configuration to enable the mss processor and also has an example project that we will work with, which also includes all the drivers you may need for a polarfire. In this project, we will showcase the process of implementing a basic “hello world” project on the eagle core polarfire soc system on module (som). As the name implies, the discovery kit targets those just setting out on their journey with polarfire soc parts — bringing down the barrier to entry with a far lower purchase price than its predecessors. In this workflow, you perform these tasks: set up your polarfire soc hardware and tools. partition your design for hardware and software implementation. generate an hdl ip core by using hdl workflow advisor. integrate the ip core into a microchip libero project and program the polarfiresoc hardware.

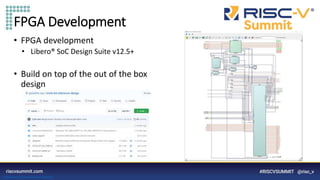

Developing For Polar Fire Soc Pptx It has the base configuration to enable the mss processor and also has an example project that we will work with, which also includes all the drivers you may need for a polarfire. In this project, we will showcase the process of implementing a basic “hello world” project on the eagle core polarfire soc system on module (som). As the name implies, the discovery kit targets those just setting out on their journey with polarfire soc parts — bringing down the barrier to entry with a far lower purchase price than its predecessors. In this workflow, you perform these tasks: set up your polarfire soc hardware and tools. partition your design for hardware and software implementation. generate an hdl ip core by using hdl workflow advisor. integrate the ip core into a microchip libero project and program the polarfiresoc hardware.

Developing For Polar Fire Soc Pptx As the name implies, the discovery kit targets those just setting out on their journey with polarfire soc parts — bringing down the barrier to entry with a far lower purchase price than its predecessors. In this workflow, you perform these tasks: set up your polarfire soc hardware and tools. partition your design for hardware and software implementation. generate an hdl ip core by using hdl workflow advisor. integrate the ip core into a microchip libero project and program the polarfiresoc hardware.

Comments are closed.