Ddr3 Memory Interface High Performance Demo

Design And Verification Of High Performance Memory Interface Based On Ddr3 memory interface: high performance demo rambus innovations enable our ddr3 phy solution to support data rates of up to 1866 megatransfers per second (mt s) in a low cost wire bond package. strategic marketing director rob dhat shows the test chip in action. Rambus innovations enable our ddr3 phy solution to support data rates of up to 1866 megatransfers per second (mt s) in a low cost wire bond package.

Ddr3 Memory Interface High Performance Demo Rambus The lattice ddr3 memory interface demonstrates the functionality of ddr3 sdram controller ip at core speed of 400mhz and 800mbps. These ddr3 sdram ip functions offer a half rate interface to the customer application logic. the parameter editor generates a design example that instantiates an example driver and your ddr3 sdram high performance controller custom variation. the design example is a fully functional design that can be simulated, synthesized, and used in hardware. Provides information about using, customizing, and simulating a logicore™ ip memory interface core for the virtex 6 fpga. serves as a technical reference to using, customizing, and simulating ddr3 and ddr2 sdram, rldram ii, rldram 3, qdrii , and lpddr2 memory interface cores. This ddr3 controller was originally designed to be used on the 10 gigabit ethernet project for an 8 lane x8 ddr3 module running at 800 mhz ddr, but this is now being designed to be a more general purpose ddr3 memory controller with multiple supported fpga boards.

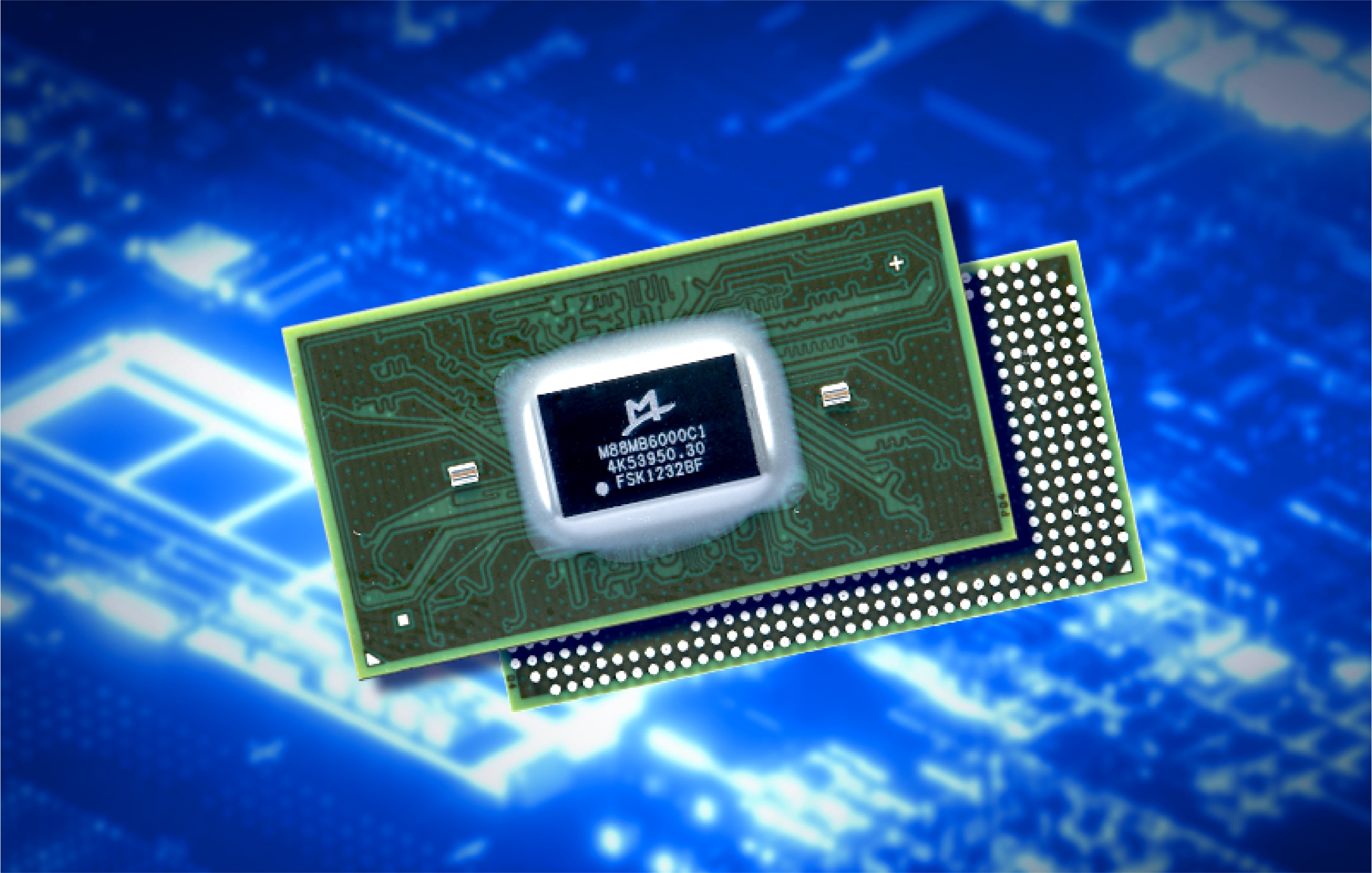

Memory Interface Montage Technology Provides information about using, customizing, and simulating a logicore™ ip memory interface core for the virtex 6 fpga. serves as a technical reference to using, customizing, and simulating ddr3 and ddr2 sdram, rldram ii, rldram 3, qdrii , and lpddr2 memory interface cores. This ddr3 controller was originally designed to be used on the 10 gigabit ethernet project for an 8 lane x8 ddr3 module running at 800 mhz ddr, but this is now being designed to be a more general purpose ddr3 memory controller with multiple supported fpga boards. Step by step guide for fpga hw design of microblaze soft processor using ddr3 sdram. find this and other hardware projects on hackster.io. Using cadence high throughput emulation technology, design and verification teams can rapidly bring up, verify, debug, and turn around their hardware and software designs using realistic system level environments. In this tutorial we are going to set up an interface to the ddr3 memory with the fpga on the alchitry au or pt. the first step is to create a project. open alchitry labs, and create a new project based on the ddr3 base project. i called mine ddr demo, but feel free to name yours whatever you want. Interfacing ddr3 sdram with a ddr3 controller involves selecting a compatible mpu fpga controller, understanding ddr3 specifications, and interfacing the ddr3 sdram according to its datasheet.

Rambus Expands Industry Leading Memory Interface Chip Offering To High Step by step guide for fpga hw design of microblaze soft processor using ddr3 sdram. find this and other hardware projects on hackster.io. Using cadence high throughput emulation technology, design and verification teams can rapidly bring up, verify, debug, and turn around their hardware and software designs using realistic system level environments. In this tutorial we are going to set up an interface to the ddr3 memory with the fpga on the alchitry au or pt. the first step is to create a project. open alchitry labs, and create a new project based on the ddr3 base project. i called mine ddr demo, but feel free to name yours whatever you want. Interfacing ddr3 sdram with a ddr3 controller involves selecting a compatible mpu fpga controller, understanding ddr3 specifications, and interfacing the ddr3 sdram according to its datasheet.

How To Design A High Speed Memory Interface Techsource Systems In this tutorial we are going to set up an interface to the ddr3 memory with the fpga on the alchitry au or pt. the first step is to create a project. open alchitry labs, and create a new project based on the ddr3 base project. i called mine ddr demo, but feel free to name yours whatever you want. Interfacing ddr3 sdram with a ddr3 controller involves selecting a compatible mpu fpga controller, understanding ddr3 specifications, and interfacing the ddr3 sdram according to its datasheet.

Comments are closed.