Counter Cache In Multiprocessor Systems Pdf Multi Core Processor

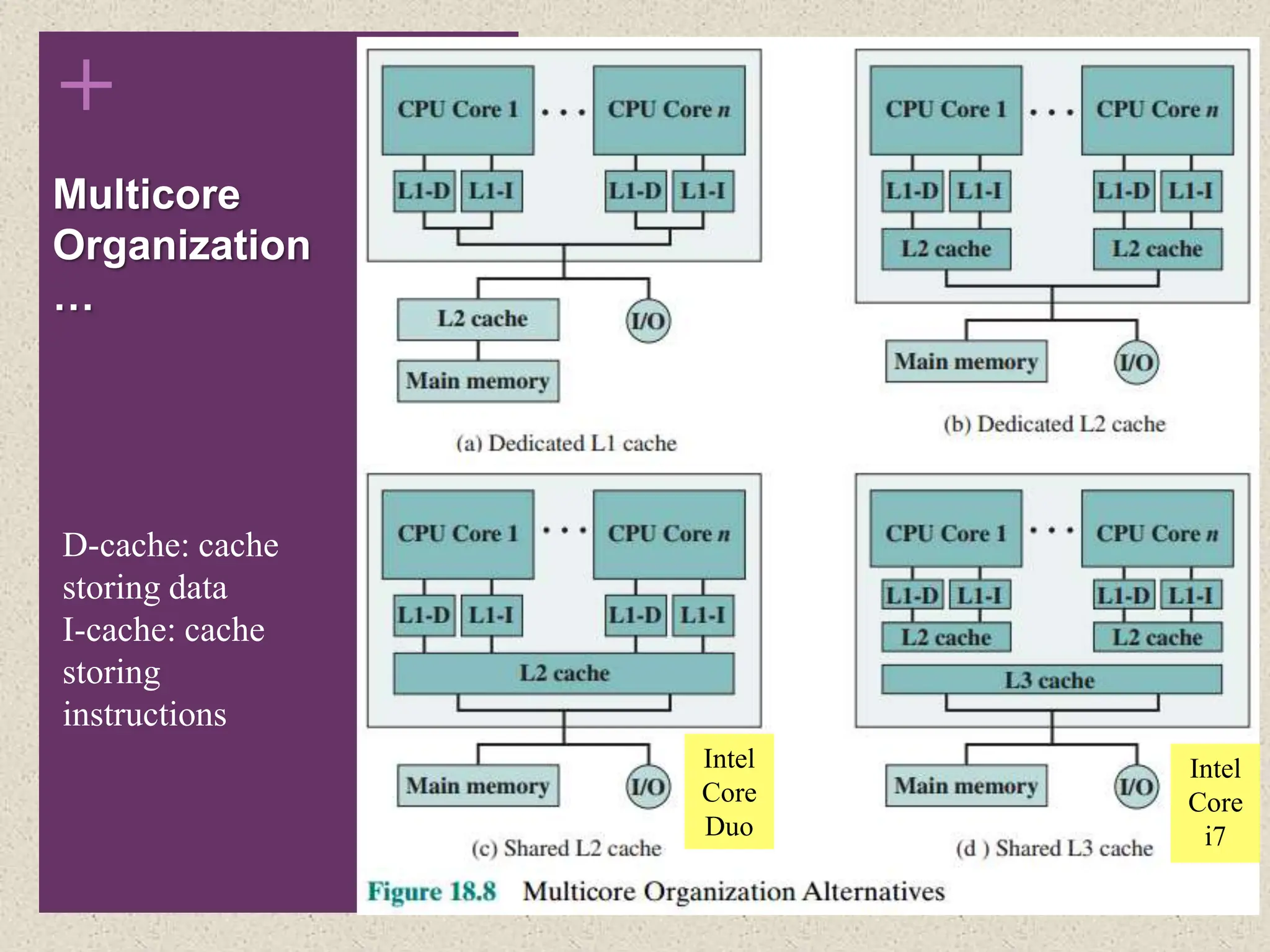

Slot29 Ch18 Multicorecomputers 18 Slides 1 Pptx This article explores the intricacies of cache coherence protocols, their implementation, and their impact on system performance. the evolution of multi core processors has necessitated sophisticated cache coherency mechanisms. Typical modern microprocessors are currently built with multicore architecture that will involve data transfers between from one cache to another. by applying cache coherence protocols to each of the caches, the coherency problem can be solved.

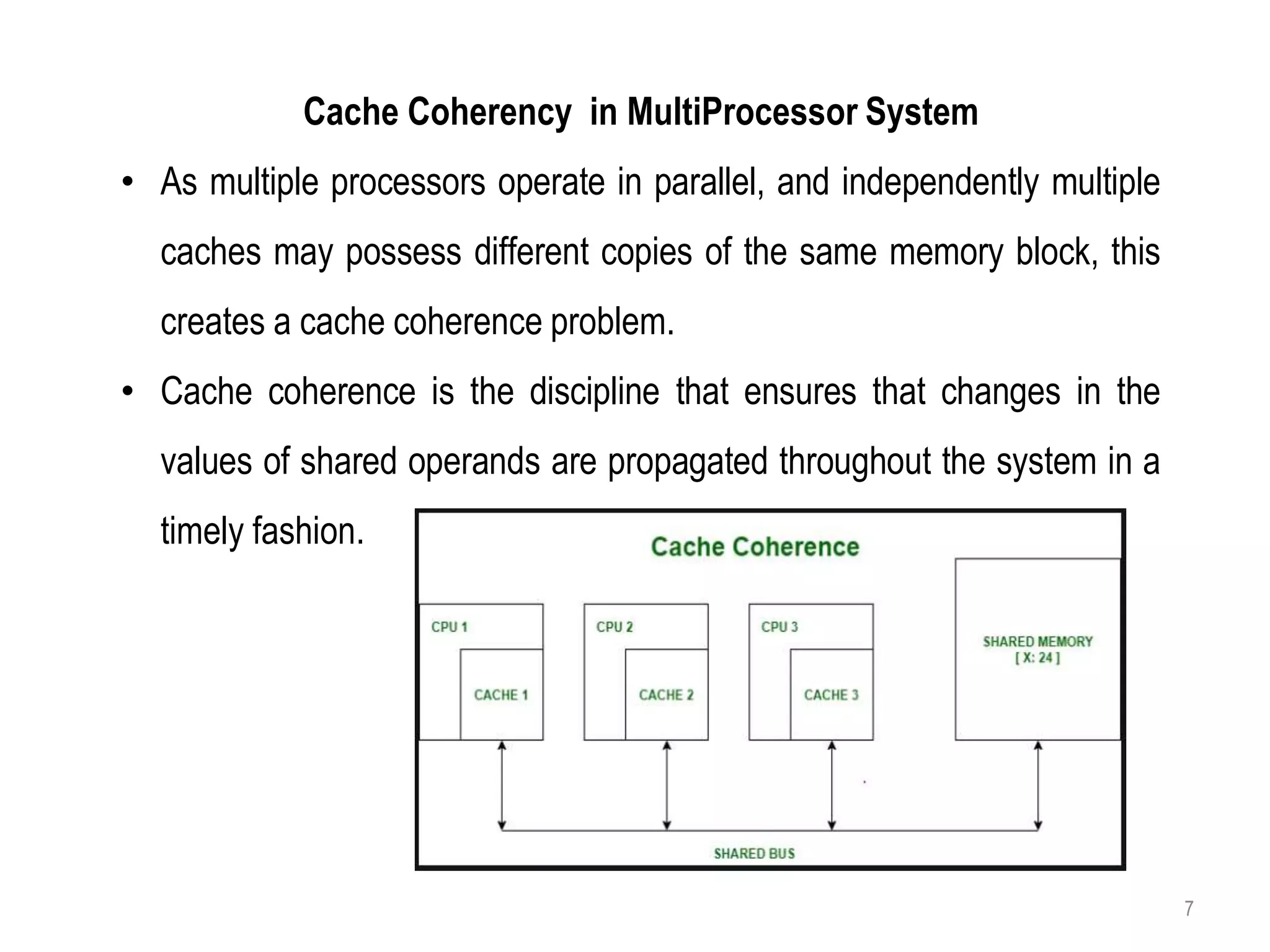

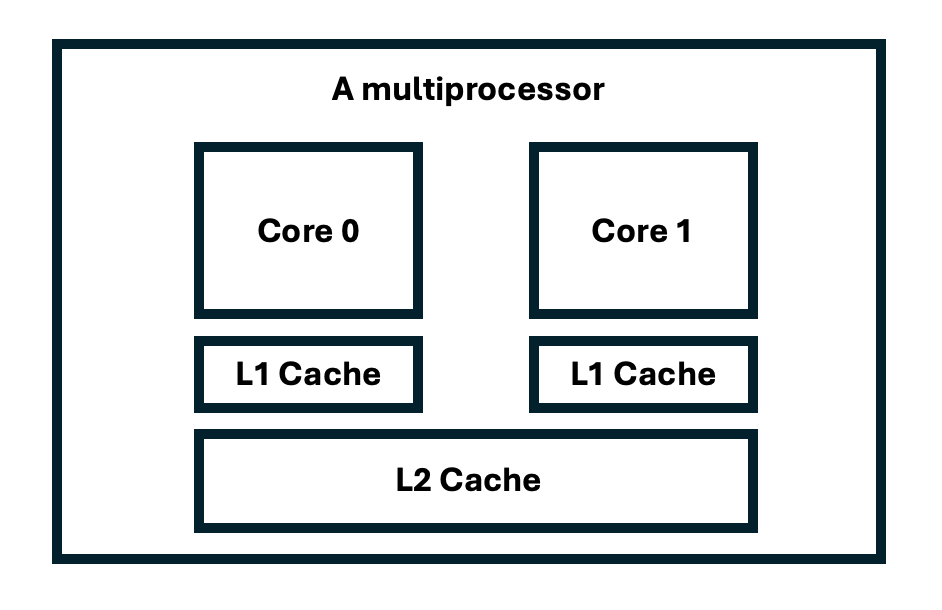

Memory And Cache Coherence In Multiprocessor System Pdf Abstract cache coherence is a fundamental requirement in shared memory multiprocessor systems where multiple processors access and modify shared data concurrently. with the increasing adoption of multicore architecture, efficient coherence mechanisms have become essential to ensure data consistency and high system performance. Multiple processors with private caches (indicated with $) are placed on a shared bus. all coherence related activity is broadcast to all processor caches through the shared bus. Problem. this report discusses three important cache coherence protocols: msi, mesi, and mesif. we model these cache coherence protocols as a markov chain model and measure the optimality. Future multi core processors will have many large cache banks connected by a network and shared by many cores. hence, many important problems must be solved: cache resources must be allocated across many cores, data must be place.

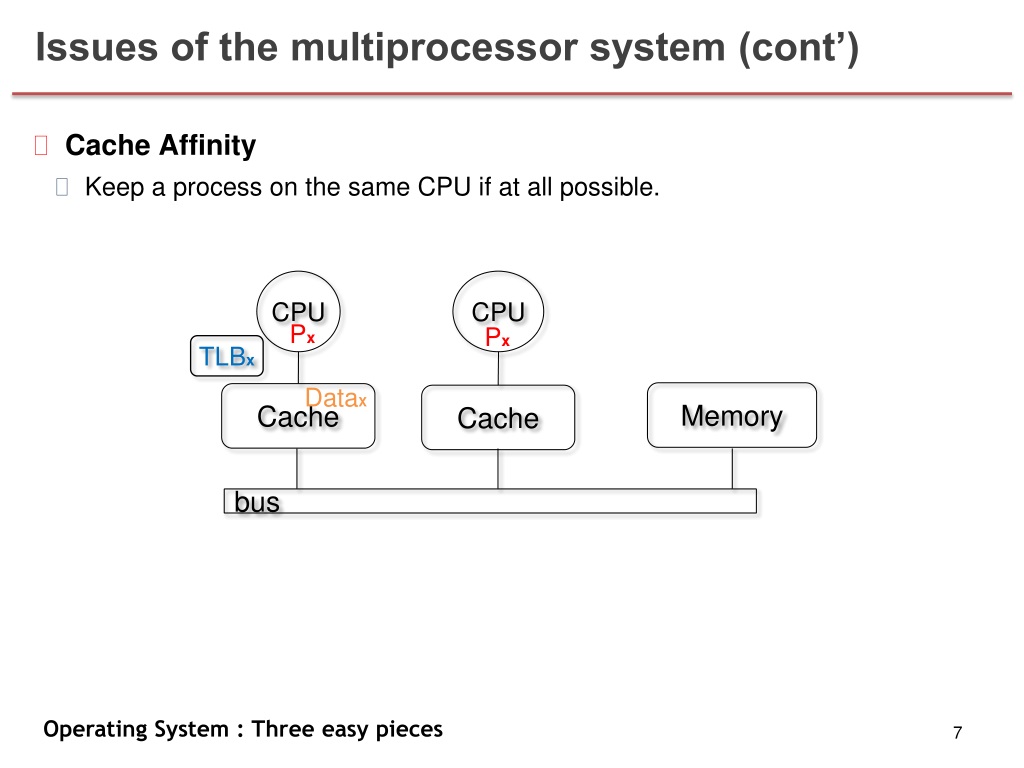

Cpu Architecture And Concurrency Home Page Problem. this report discusses three important cache coherence protocols: msi, mesi, and mesif. we model these cache coherence protocols as a markov chain model and measure the optimality. Future multi core processors will have many large cache banks connected by a network and shared by many cores. hence, many important problems must be solved: cache resources must be allocated across many cores, data must be place. Imagine a two core processor using the msi coherence protocol. for each question below, assume that a single line exists in both processors’ caches, but possibly in different coherence states. The document discusses the significance of cache hierarchies in multi core processors, emphasizing their impact on system performance and power dissipation. it highlights the need to enhance on chip cache efficiency to reduce off chip memory access, which consumes more cycles and energy. Parallel systems architecture is a vast topic, and we can only scratch the surface. the critical things i hope you will learn from this very brief introduction are: why is shared memory parallel programming attractive? how is dynamic load balancing implemented?. Cache coherence protocols will cause mutex to ping pong between p1’s and p2’s caches. ping ponging can be reduced by first reading the mutex location (non atomically) and executing a swap only if it is found to be zero (test&test&set). thank you!.

Counter Cache In Multiprocessor Systems Pdf Multi Core Processor Imagine a two core processor using the msi coherence protocol. for each question below, assume that a single line exists in both processors’ caches, but possibly in different coherence states. The document discusses the significance of cache hierarchies in multi core processors, emphasizing their impact on system performance and power dissipation. it highlights the need to enhance on chip cache efficiency to reduce off chip memory access, which consumes more cycles and energy. Parallel systems architecture is a vast topic, and we can only scratch the surface. the critical things i hope you will learn from this very brief introduction are: why is shared memory parallel programming attractive? how is dynamic load balancing implemented?. Cache coherence protocols will cause mutex to ping pong between p1’s and p2’s caches. ping ponging can be reduced by first reading the mutex location (non atomically) and executing a swap only if it is found to be zero (test&test&set). thank you!.

Ppt Multiprocessor Scheduling Advanced Powerpoint Presentation Parallel systems architecture is a vast topic, and we can only scratch the surface. the critical things i hope you will learn from this very brief introduction are: why is shared memory parallel programming attractive? how is dynamic load balancing implemented?. Cache coherence protocols will cause mutex to ping pong between p1’s and p2’s caches. ping ponging can be reduced by first reading the mutex location (non atomically) and executing a swap only if it is found to be zero (test&test&set). thank you!.

Comments are closed.