Configurable Risc V On Fpga

A Configurable Risc V Processor Core For Fpga Devices Pdf Central Due to these features, risc v has been adopted in the industry and has taken a significant share of the market. the flexibility of risc v allows for a variety of different hardware implementations. this project takes advantage of this flexibility to create a customizable processor core for reprogrammable devices. This paper introduces the design and fpga based implementation of a compact and power efficient 32 bit processor based on the risc v instruction set architecture, tailored for resource constrained embedded systems.

Risc V Fpga In this project you will learn how to implement a risc v processor in a smartfusion2 soc. find this and other hardware projects on hackster.io. This plugin implements the multiplication, division and modulo of the risc v m extension in an iterative way, which is friendly for small fpgas that don't have dsp blocks. Here's a project that demonstrates the advantage of having an opensource instruction set (risc v) along with the power of being able to wire an fpga into one. this project implements a minimal risc v core in an icefun fpga board. This paper presents the design and implementation of a 32 bit, in order, 5 stage pipelined risc v processor, executed on the basys 3 artix 7 fpga. risc v, an op.

Github Superchamp234 Risc V Fpga Implementing A Risc V Cpu On Fpga Here's a project that demonstrates the advantage of having an opensource instruction set (risc v) along with the power of being able to wire an fpga into one. this project implements a minimal risc v core in an icefun fpga board. This paper presents the design and implementation of a 32 bit, in order, 5 stage pipelined risc v processor, executed on the basys 3 artix 7 fpga. risc v, an op. The entire design is synthesized and implemented on a spartan 6 fpga board. this project demonstrates the feasibility and effectiveness of implementing a single cycle risc v processor on fpga, providing valuable insights into processor design and hardware implementation. To reduce the overhead of the embedded processor as much as possible, this paper designs and implements a configurable 32 bit in order risc v processor core based on the 16 bit data path and. The main goal of this work is the development of a risc v softcore processor to be implemented in an fpga, using a non risc v core as the base of this architecture. It is both fully risc v double precision and ieee 754 compliant and offers reduced latency compared to existing designs as well as compile time configurable precision, for applications with relaxed precision requirements.

Github Superchamp234 Risc V Fpga Implementing A Risc V Cpu On Fpga The entire design is synthesized and implemented on a spartan 6 fpga board. this project demonstrates the feasibility and effectiveness of implementing a single cycle risc v processor on fpga, providing valuable insights into processor design and hardware implementation. To reduce the overhead of the embedded processor as much as possible, this paper designs and implements a configurable 32 bit in order risc v processor core based on the 16 bit data path and. The main goal of this work is the development of a risc v softcore processor to be implemented in an fpga, using a non risc v core as the base of this architecture. It is both fully risc v double precision and ieee 754 compliant and offers reduced latency compared to existing designs as well as compile time configurable precision, for applications with relaxed precision requirements.

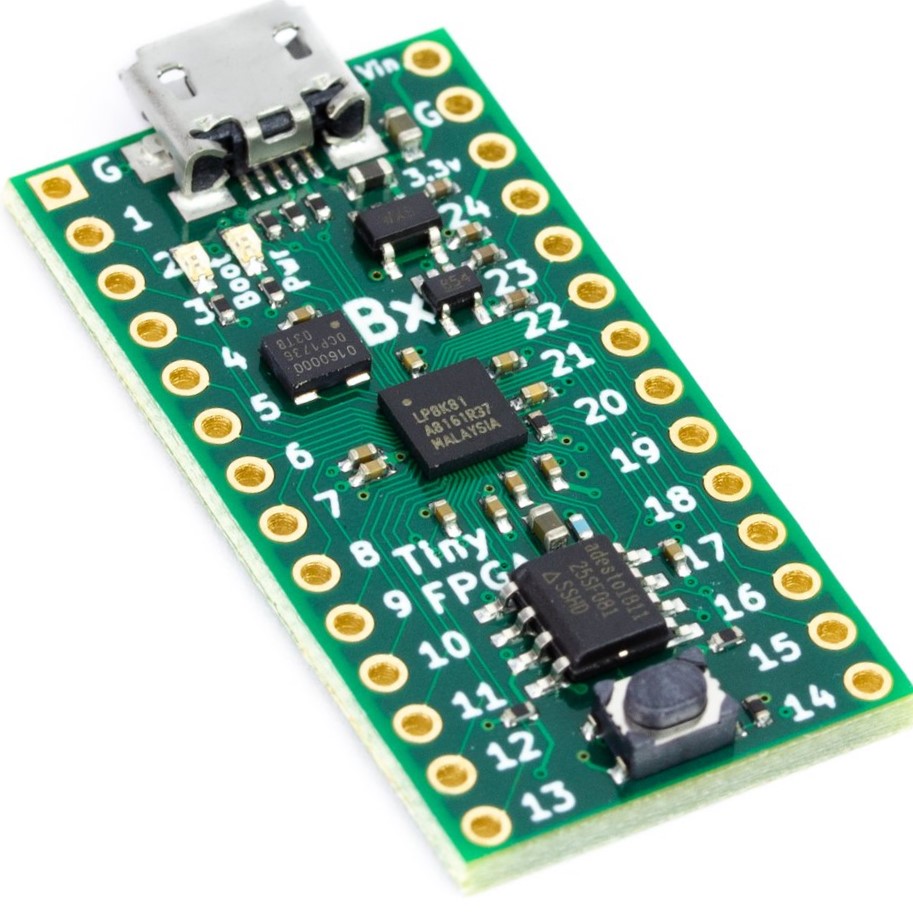

Risc V Processor On Tinyfpga Bx Fpga Ethernet Cores The main goal of this work is the development of a risc v softcore processor to be implemented in an fpga, using a non risc v core as the base of this architecture. It is both fully risc v double precision and ieee 754 compliant and offers reduced latency compared to existing designs as well as compile time configurable precision, for applications with relaxed precision requirements.

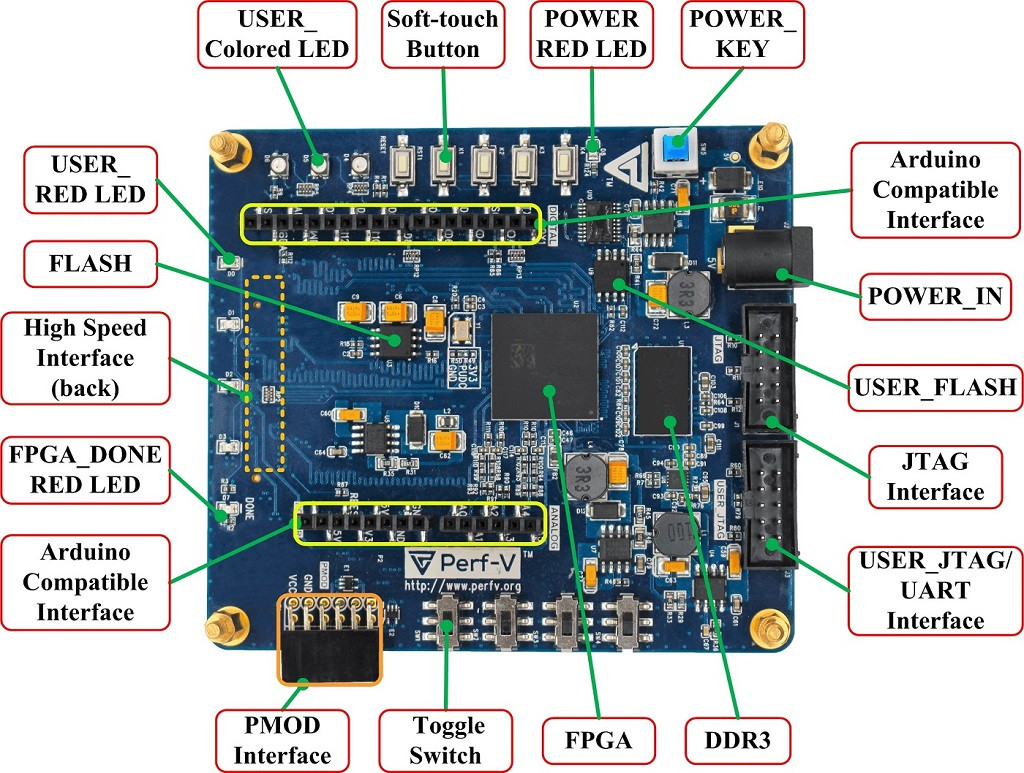

Perf V Fpga Based Risc V Development Board Electronics Lab

Comments are closed.