Configurable Deadtime

Deadtime Generator Platform For Creating And Sharing Projects Oshwlab This video provides a high level overview of the configurable dead time feature. learn about the feature, benefits, and drawbacks for a system. The maximum configurable deadtime rising falling value is 511, but in our example, we configure it to 200. the deadtime calculations for different prescaler values, based on the configured deadtime value of 200, are shown below:.

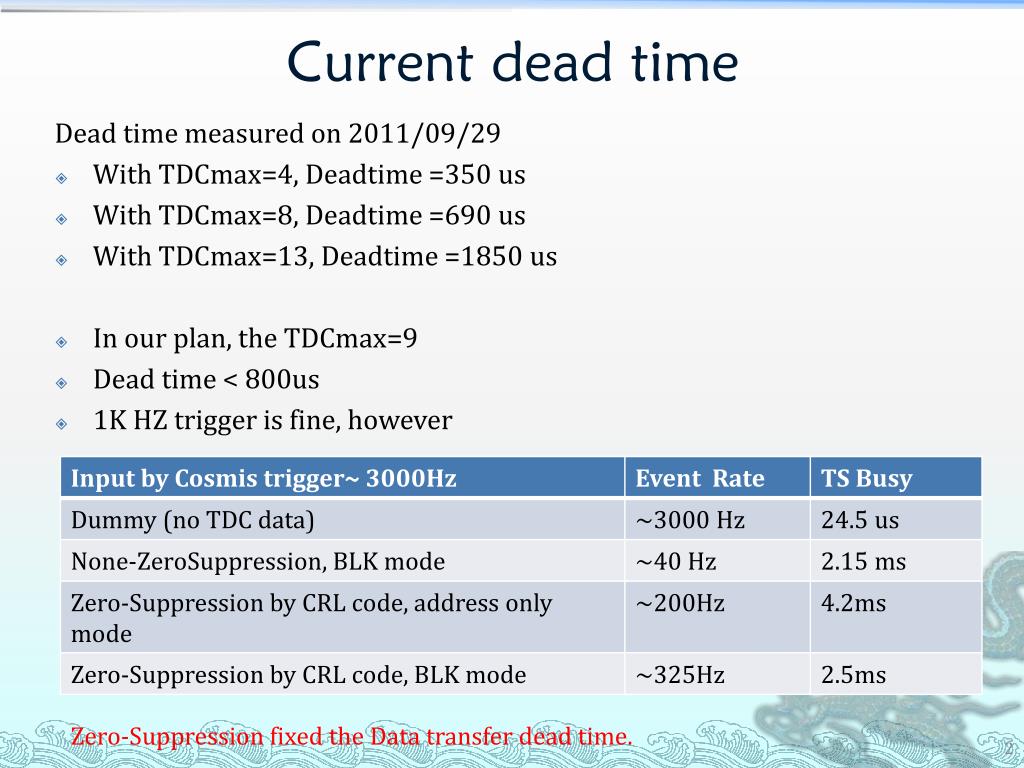

Ppt Optimal Dead Time Reduction Strategy For Data Acquisition Systems A configurable pulse width modulation (pwm) generator ip core written in systemverilog. this module is designed for use in digital control systems for power electronics applications like motor drives, dc dc converters, and inverters, where preventing signal overlap is critical. The second feature covered in this video series is the configurable deadtime. this is a feature that can help to increase the robustness and safety of your system. In conclusion, we’ve explored the stm32 complementary pwm output mode, how it works, and how to configure the stm32 advanced control timer to generate complementary pwm signals with configurable frequency, duty cycle, and dead time insertion. Dead time (also known as blanking time) is a short, intentional delay inserted between the turn off command of one switch in a complementary pair and the turn on command of the other switch.

A The Csc Induced Deadtime And Complex Deadtime With Run 2 Occupancy In conclusion, we’ve explored the stm32 complementary pwm output mode, how it works, and how to configure the stm32 advanced control timer to generate complementary pwm signals with configurable frequency, duty cycle, and dead time insertion. Dead time (also known as blanking time) is a short, intentional delay inserted between the turn off command of one switch in a complementary pair and the turn on command of the other switch. By using oscilloscope and probing both pa7 and pa8, we shall get the following: the cursor measures a dead time of 62us which is near the calculated value of 63us. with this, you have successfully generated deadtime for two pwm signal and can be implemented in ton of applications. happy coding. Deadtime prevents both complementary outputs from being simultaneously active, which would create a short circuit in typical power converter topologies. the hrtim inserts configurable delays on both rising and falling edges of output transitions. I'd like to make a gating controller for two igbts, with configurable deadtime and variable frequency. at this moment, the frequency is fixed, and it is implemented as follows, using two voltage sources:. For reliability, it should be long enough to avoid the shoot through. this vhdl design can generate the control signals for the two transistors, and gives a very fine control over the dead time (resolution: one clock tick). you can precisely define it, and guarantee that it's always there. the pwm block has these inputs and outputs:.

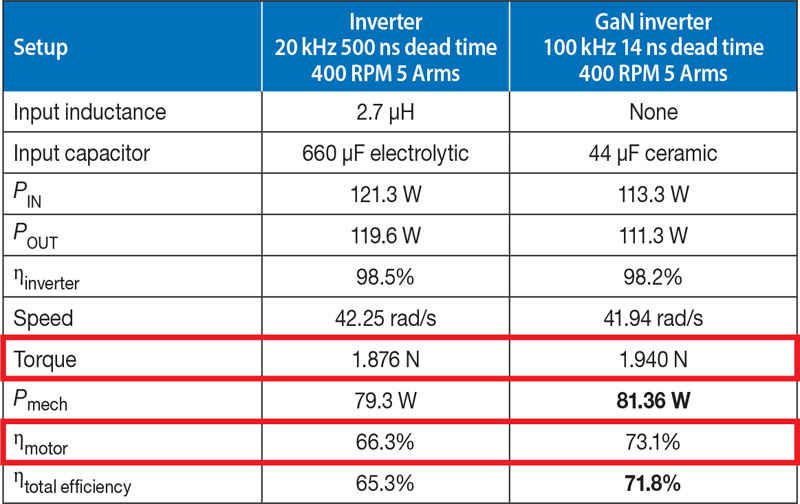

Time To Kill The Deadtime By using oscilloscope and probing both pa7 and pa8, we shall get the following: the cursor measures a dead time of 62us which is near the calculated value of 63us. with this, you have successfully generated deadtime for two pwm signal and can be implemented in ton of applications. happy coding. Deadtime prevents both complementary outputs from being simultaneously active, which would create a short circuit in typical power converter topologies. the hrtim inserts configurable delays on both rising and falling edges of output transitions. I'd like to make a gating controller for two igbts, with configurable deadtime and variable frequency. at this moment, the frequency is fixed, and it is implemented as follows, using two voltage sources:. For reliability, it should be long enough to avoid the shoot through. this vhdl design can generate the control signals for the two transistors, and gives a very fine control over the dead time (resolution: one clock tick). you can precisely define it, and guarantee that it's always there. the pwm block has these inputs and outputs:.

The Circuit Used To Estimate The Deadtime Download Scientific Diagram I'd like to make a gating controller for two igbts, with configurable deadtime and variable frequency. at this moment, the frequency is fixed, and it is implemented as follows, using two voltage sources:. For reliability, it should be long enough to avoid the shoot through. this vhdl design can generate the control signals for the two transistors, and gives a very fine control over the dead time (resolution: one clock tick). you can precisely define it, and guarantee that it's always there. the pwm block has these inputs and outputs:.

Comments are closed.