Combinational Logic Parity Checker

Parity Checker Pdf Bit Arithmetic A parity generator circuit is a combinational logic circuit that is used at the transmitting end. its primary function is to calculate and add the parity bit to the data stream based on the chosen parity scheme (even or odd). A parity generator is a combinational logic circuit used to generate and add a parity to the input or transmitted data, while a parity checker is also a combinational circuit used to verify the correctness of received data.

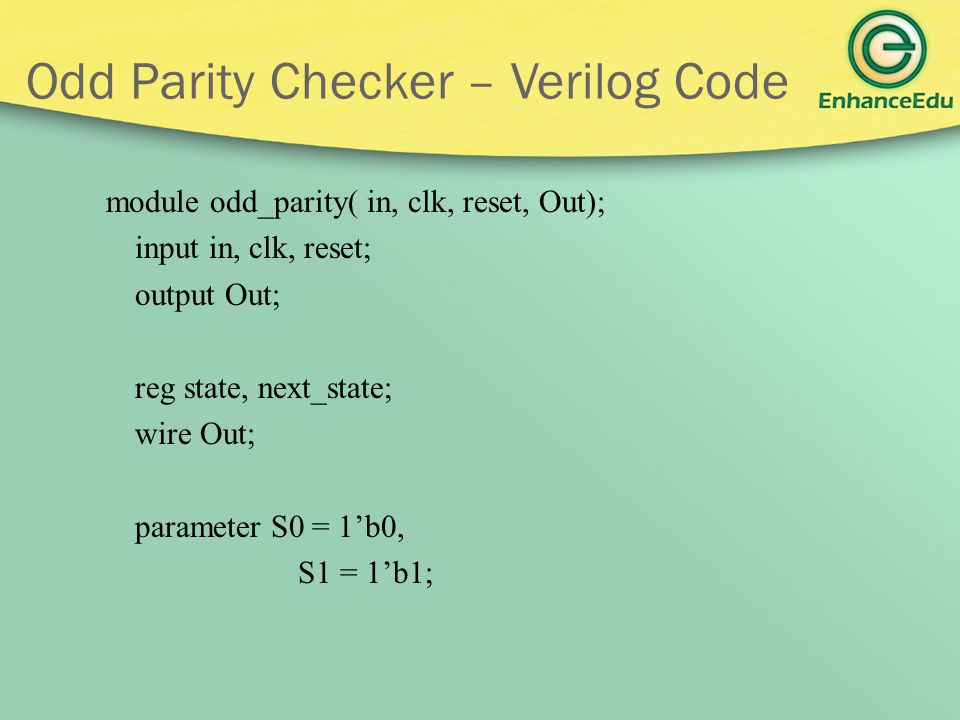

Combinational Logic Design Parity Generator Checker Q Parity In this article, how the parity generator and checker generate and check the bit and its types, logic circuits, truth tables, and k map expressions are discussed briefly. A parity generator is a combinational logic circuit that generates the parity bit in the transmitter. on the other hand, a circuit that checks the parity in the receiver is called parity checker. A parity checker is a combinational logic circuit that checks the parity of the received data word at the receiver end. it takes the data word with the appended parity bit as input and outputs a signal that indicates whether there is an error or not. This video describes how to design a parity checker. an example using 3 bit data (plus the parity bit) is used, but the process can be applied to any number.

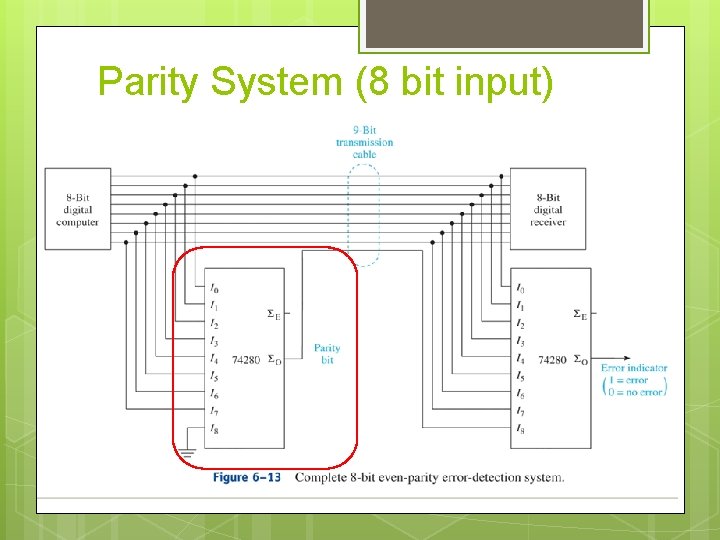

Ppt Combinational Logic And Verilog Powerpoint 54 Off A parity checker is a combinational logic circuit that checks the parity of the received data word at the receiver end. it takes the data word with the appended parity bit as input and outputs a signal that indicates whether there is an error or not. This video describes how to design a parity checker. an example using 3 bit data (plus the parity bit) is used, but the process can be applied to any number. The parity checker circuit is a practical example of using combinational logic gates as an error detection system. the circuit turns on the led only when it detects an error, which occurs when the input bits have an odd number of 1s. To avoid problems caused by unwanted data corruption, a parity generator checker system, like the one shown in fig can be used. the basic idea is to add an extra bit, called a parity bit, to the digital information being transmitted. The document provides examples of how parity bits are generated and used to detect errors. it also discusses applications of parity including in data transmission and memory caches. A parity generator is a combinational logic circuit that generates the parity bit in the transmitter. on the other hand, a circuit that checks the parity in the receiver is called parity checker.

Comments are closed.