Centralized Shared Memory Architectures Pdf

L39 Centralized Shared Memory Architectures Pdf Cpu Cache Cache This document discusses centralized shared memory architectures and cache coherence protocols. it begins by explaining how multiple processors can share memory through a shared bus and cached data. Centralized shared memory architectures tivates centralized memory multiprocessors. originally, these processors were all single core and often took an entire bo.

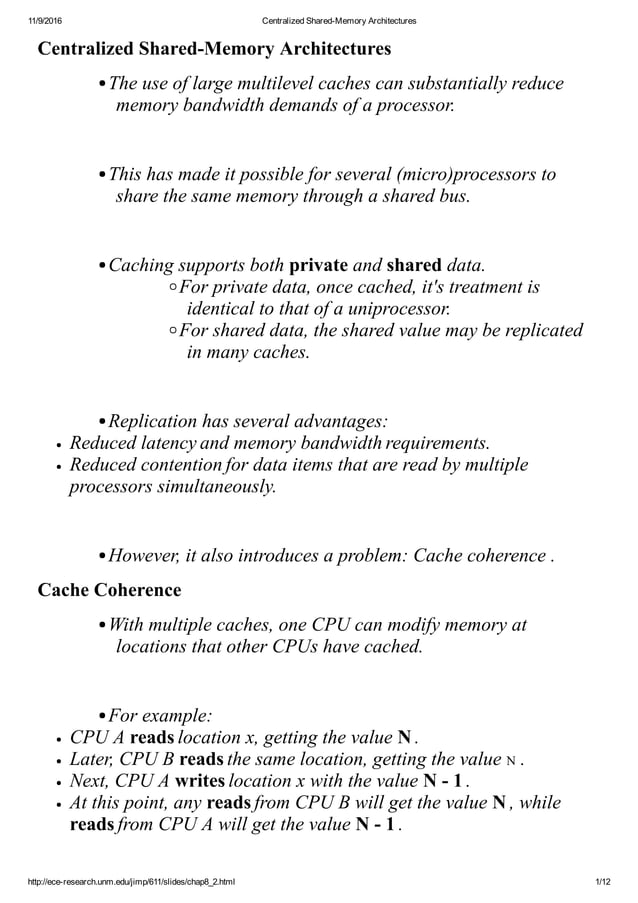

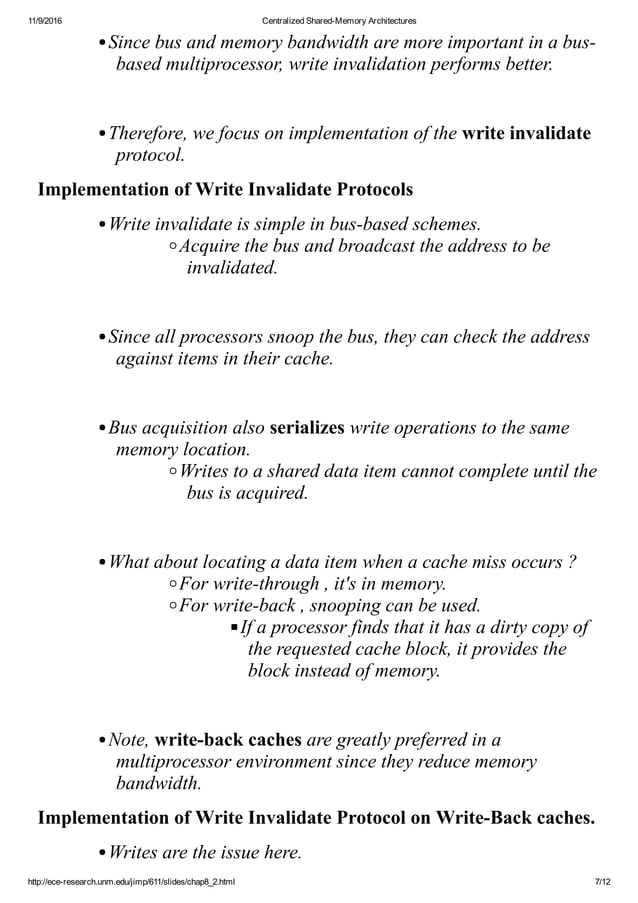

Shared Memory Architecture Pdf L39 centralized shared memory architectures free download as powerpoint presentation (.ppt .pptx), pdf file (.pdf), text file (.txt) or view presentation slides online. Chapter 12: multiprocessor architectures lesson 06: centralized shared memory architecture. This can be tracked by adding an extra state bit (in addition to the valid and dirty bits) that indicates if the block is shared. if the bit is set (the block is shared), the cache generates an invalidation on the bus and marks the block as private. Shared memory systems two variants: shared cache systems separate cache, bus based access to shared memory.

0014 Sharedmemoryarchitecture Pdf Cache Computing Computer This can be tracked by adding an extra state bit (in addition to the valid and dirty bits) that indicates if the block is shared. if the bit is set (the block is shared), the cache generates an invalidation on the bus and marks the block as private. Shared memory systems two variants: shared cache systems separate cache, bus based access to shared memory. Cache coherence in shared memory architectures adapted from a lecture by ian watson, university of machester. The problem of building and managing updates in a memory hierarchy for a shared memory multiprocessor is complicated by the processor local (cache) memories, the global memory, and the delays and order of memory reading and writing to the memory hierarchy. Because access to shared memory is balanced, these systems are also called smp (symmetric multiprocessor) systems. each processor has equal opportunity to read write to memory, including equal access speed. Mimd processors share a single centralized memory through a bus interconnect feasible for small processor count to limit memory contention caches serve to: increase bandwidth versus bus memory reduce latency of access.

Centralized Shared Memory Architectures Pdf Cache coherence in shared memory architectures adapted from a lecture by ian watson, university of machester. The problem of building and managing updates in a memory hierarchy for a shared memory multiprocessor is complicated by the processor local (cache) memories, the global memory, and the delays and order of memory reading and writing to the memory hierarchy. Because access to shared memory is balanced, these systems are also called smp (symmetric multiprocessor) systems. each processor has equal opportunity to read write to memory, including equal access speed. Mimd processors share a single centralized memory through a bus interconnect feasible for small processor count to limit memory contention caches serve to: increase bandwidth versus bus memory reduce latency of access.

Centralized Shared Memory Architectures Pdf Because access to shared memory is balanced, these systems are also called smp (symmetric multiprocessor) systems. each processor has equal opportunity to read write to memory, including equal access speed. Mimd processors share a single centralized memory through a bus interconnect feasible for small processor count to limit memory contention caches serve to: increase bandwidth versus bus memory reduce latency of access.

Centralized Shared Memory Architectures Pdf

Comments are closed.