Advancing Integration Chip Stacking Technology

Amd Discloses Its Multi Layer Chiplet Design Era Starting With Zen 3 Increasing the number of transistors you can squeeze into a given area by stacking up chips (called chiplets in this case) is both the present and future of silicon. Explore the world of 3d ic technology, enabling advanced semiconductor integration through vertical stacking for enhanced performance and reduced form factors.

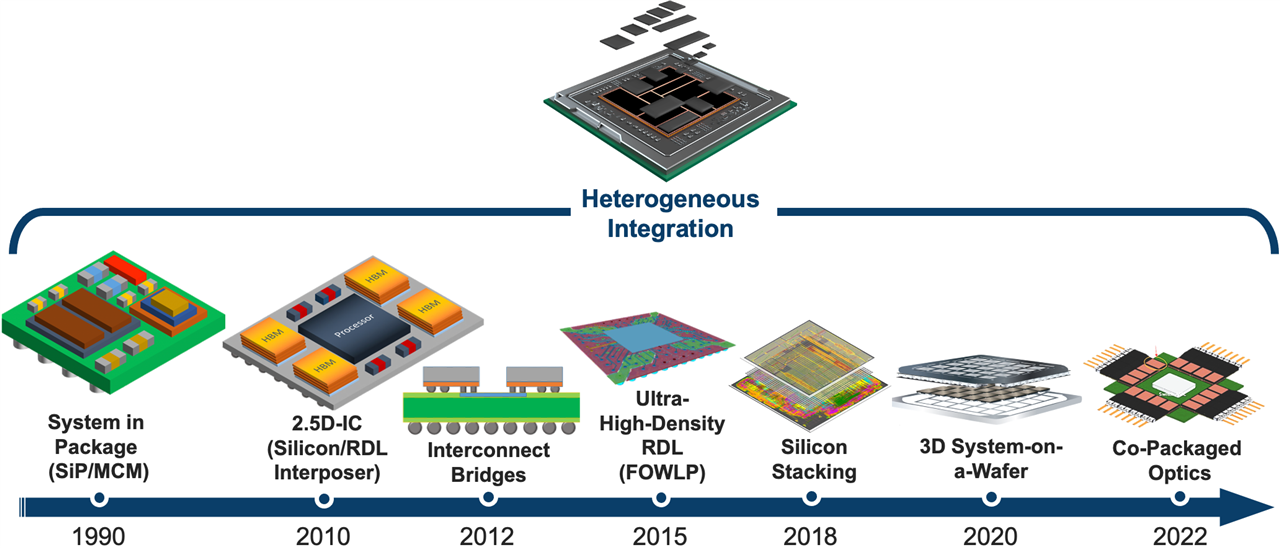

Chiplets And Heterogeneous Packaging Are Changing System Design And With the continuous reduction of chip feature size, the continuation of moore's law becomes increasingly difficult and heterogeneous integration has become one of the important orientations of electronic technology. The future of chips is vertical. we analyze 3d stacking, hybrid bonding & advanced interconnects—the technologies driving the next wave of semiconductor performance. These implementations showcase how 3d chip stacking is revolutionizing ai hardware, making advanced computing more efficient and accessible while addressing critical power and space constraints. This technology enables two transistors to be stacked and integrated into the size of a single transistor. this not only significantly increases transistor density but also simplifies the layout of cmos logic circuits, enhancing design efficiency.

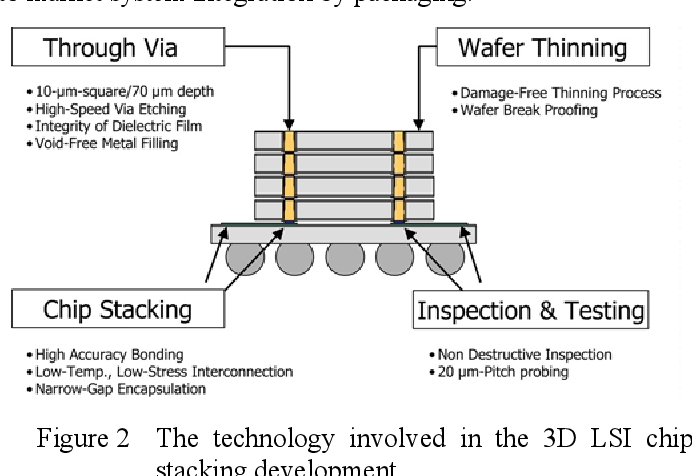

Figure 1 From Development Of Advanced 3d Chip Stacking Technology With These implementations showcase how 3d chip stacking is revolutionizing ai hardware, making advanced computing more efficient and accessible while addressing critical power and space constraints. This technology enables two transistors to be stacked and integrated into the size of a single transistor. this not only significantly increases transistor density but also simplifies the layout of cmos logic circuits, enhancing design efficiency. At the heart of this revolutionary approach lies through silicon via (tsv) technology, which facilitates electrical connections between stacked layers. this article delves into tsv technology, the challenges of stacking, and the potential benefits of 3d ic integration. Researchers can now fabricate a 3d chip with alternating layers of semiconducting material grown directly on top of each other. the method eliminates thick silicon substrates between the layers,. Explore the advancements in 3d stacking technology, a significant innovation in the semiconductor industry. learn how vertical integration of ic layers enhances chip density and performance, addressing the limitations of 2d designs. This paper delves into the concept of 3d stacked ic chip design, which offers significant advantages over planar chips, and examines the transition from cmos technology to the utilization of 2d materials.

Comments are closed.