05 Programmers Model Register Set Arm Cortex M 101

Assembly Programming For Arm Cortex M Processors Scanlibs 05 programmers model register set | arm cortex m 101 inpyjama (archieves) 20k subscribers subscribe. This short course introduces the arm m architecture based cortex m series of cpus and presents the essentials of working with m class cpus controllers. you will learn how to think and reason about these cpus.

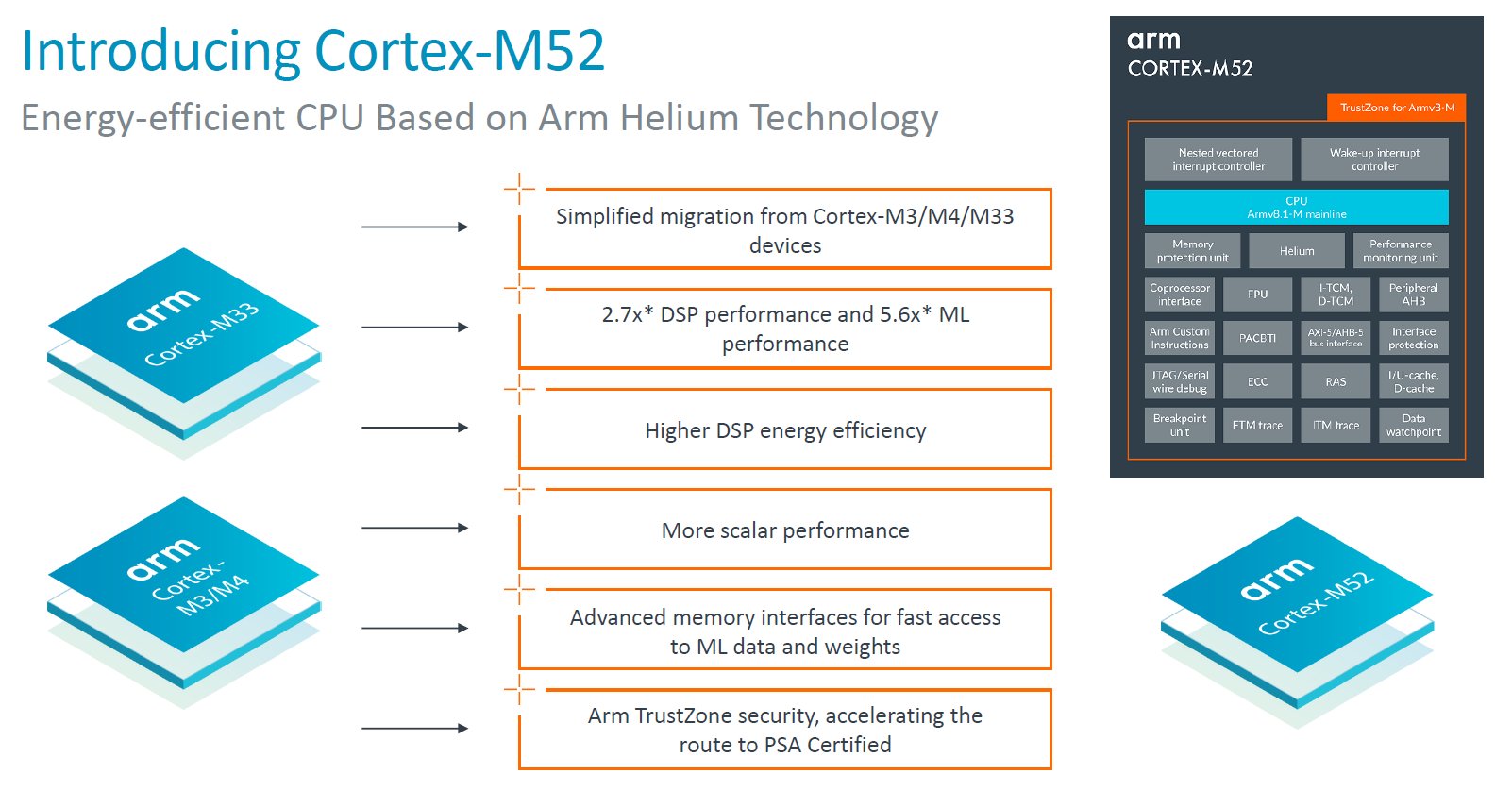

Arm Pumps Up Ai For Small Devices With Cortex M52 The Register Learn by programing the baremetal aarch64 based arm cpu using assembly and c programming. The document presents an overview of the arm programmer's model, detailing its architecture, register types, and functionality. it explains the significance of special function registers like the stack pointer, link register, and program counter, along with the current program status register (cpsr) used for condition codes. This section describes the cortex m3 programmers model. in addition to the individual core register descriptions, it contains information about the processor modes and privilege levels for software execution and stacks. This section describes the cortex m3 processor programmers model. in addition to the individual core register descriptions, it contains information about the processor modes and privilege levels for software execution and stacks.

Arm Cortex M0 M3 Register File Architecture And Multiplexer Tree This section describes the cortex m3 programmers model. in addition to the individual core register descriptions, it contains information about the processor modes and privilege levels for software execution and stacks. This section describes the cortex m3 processor programmers model. in addition to the individual core register descriptions, it contains information about the processor modes and privilege levels for software execution and stacks. Arm cortex m architecture you will learn in this module cortex m architecture buses cisc versus risc registers. We will not go through each of the various cp15 registers in detail, because this would duplicate reference information that can readily be obtained from the arm architecture reference manual or product documentation. Arm instruction set outline arm versions. arm assembly language. arm programming model. arm memory organization. Microcontroller profiles implement a programmers’ model designed for fast interrupt processing, with hardware stacking of registers and support for writing interrupt handlers in high level languages.

Arm Cortex M Assembly Programming For Embedded Programmers Using Keil Arm cortex m architecture you will learn in this module cortex m architecture buses cisc versus risc registers. We will not go through each of the various cp15 registers in detail, because this would duplicate reference information that can readily be obtained from the arm architecture reference manual or product documentation. Arm instruction set outline arm versions. arm assembly language. arm programming model. arm memory organization. Microcontroller profiles implement a programmers’ model designed for fast interrupt processing, with hardware stacking of registers and support for writing interrupt handlers in high level languages.

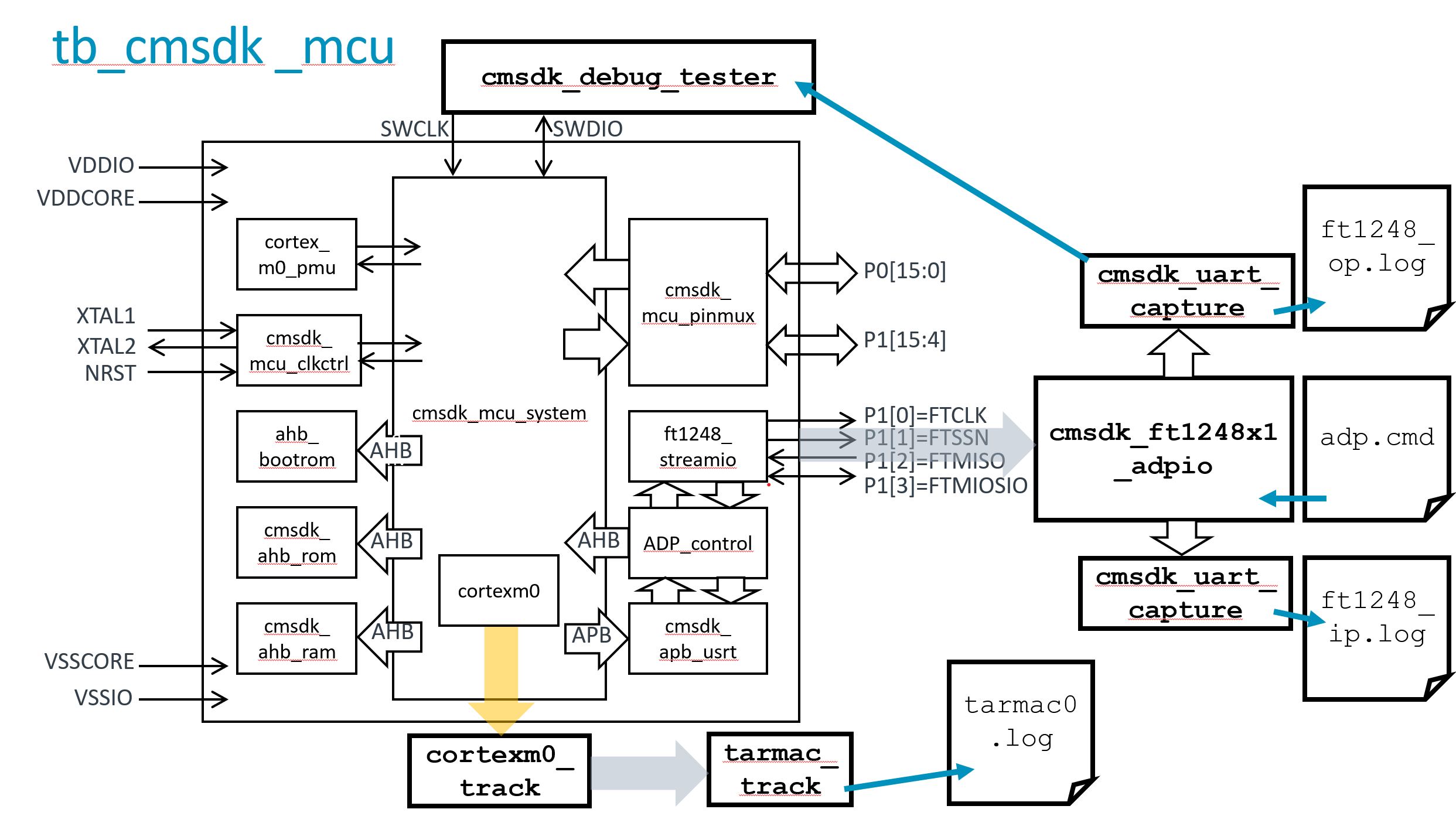

Arm Cortex M0 Microcontroller Soc Labs Arm instruction set outline arm versions. arm assembly language. arm programming model. arm memory organization. Microcontroller profiles implement a programmers’ model designed for fast interrupt processing, with hardware stacking of registers and support for writing interrupt handlers in high level languages.

Github Abdelazeem201 Microcontrollers Based On The Arm Cortex M0

Comments are closed.