04 Verification Validation Automated Code Generation For Embedded Systems

Validation Computerised Systems Version 2 0 Dec 2007 Pdf This webinar will showcase best practices for testing, validating, and deploying control algorithms efficiently using model based design. Learn the importance of validation and verification in embedded systems, and how to implement these processes effectively to ensure product reliability and quality.

Embedded Verification Validation At 1000 Day In Noida Id Model based design (mbd) is transforming industries by integrating simulation, validation, and automatic code generation into a single development workflow. It discusses the increasing complexity of real time embedded systems, particularly in automotive applications, and highlights the need for a certified code gene. To address these challenges, this paper introduces agents4plc, a novel framework that not only automates plc code generation but also includes code level verification through an llm based multi agent system. In this paper, we present a new optimizing code generation method that can deploy these operations successfully while also verifying that the generated code is a correct translation of the input program.

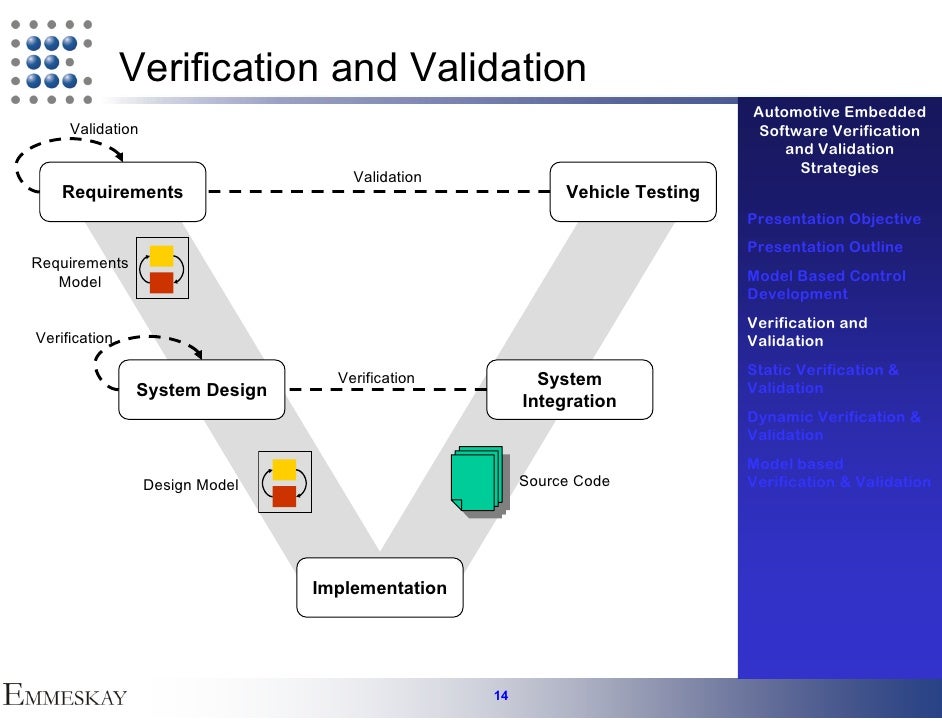

What Is Verification And Validation In Embedded System Design Inspiro To address these challenges, this paper introduces agents4plc, a novel framework that not only automates plc code generation but also includes code level verification through an llm based multi agent system. In this paper, we present a new optimizing code generation method that can deploy these operations successfully while also verifying that the generated code is a correct translation of the input program. In automotive context, the embedded software verification and validation (v&v) is always a critical step for each project that involves testing solutions for new function, system. Engineering teams use model based design with matlab and simulink to design complex embedded systems and generate production quality c, c , and hdl code. It discusses the increasing complexity of real time embedded systems, particularly in automotive applications, and highlights the need for a certified code generator capable of transforming matlab simulink and stateflow models into validated vhdl code. Verification vs validation in embedded software is a hot topic in the software development space. while both terms portray similar meanings, there are noteworthy differences. check out this post to learn them.

Ecu Verification Validation In automotive context, the embedded software verification and validation (v&v) is always a critical step for each project that involves testing solutions for new function, system. Engineering teams use model based design with matlab and simulink to design complex embedded systems and generate production quality c, c , and hdl code. It discusses the increasing complexity of real time embedded systems, particularly in automotive applications, and highlights the need for a certified code generator capable of transforming matlab simulink and stateflow models into validated vhdl code. Verification vs validation in embedded software is a hot topic in the software development space. while both terms portray similar meanings, there are noteworthy differences. check out this post to learn them.

Electronics Special Issue Software Verification And Validation For It discusses the increasing complexity of real time embedded systems, particularly in automotive applications, and highlights the need for a certified code generator capable of transforming matlab simulink and stateflow models into validated vhdl code. Verification vs validation in embedded software is a hot topic in the software development space. while both terms portray similar meanings, there are noteworthy differences. check out this post to learn them.

Comments are closed.