Xilinx Ise Design And Simulate Verilog Hdl Code

Hdl Design Using Verilog Pdf Learn to simulate your digital designs using xilinx ise. this short video will save lots of time and will help you to start the simulation within minutes. Creating a vhdl simulation model allows you to accurately simulate the behavior of a verilog module from a vhdl context. note: this step is required only if you plan to simulate component level ip in a third party simulator such as xilinx isim.

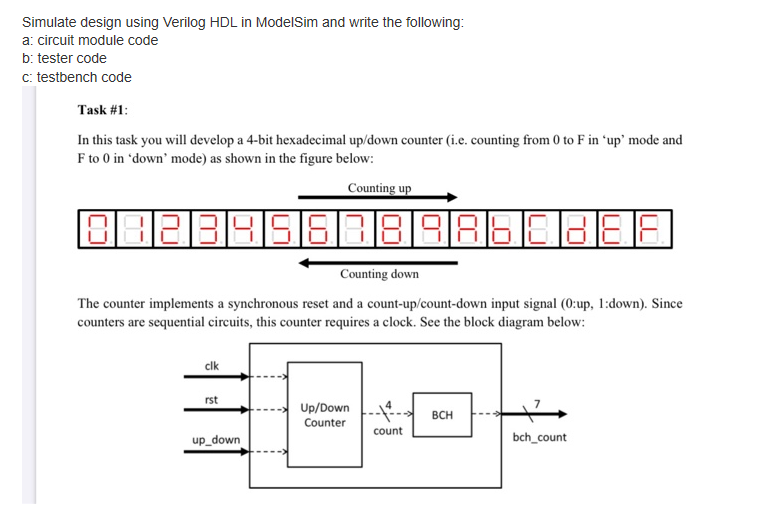

Buy A Tutorial On Fpga Based System Design Using Verilog Hdl Xilinx Simulate your circuit using the ise simulator and a verilog testbench to provide inputs to the circuit. use “if” statements in your testbench to make it self checking. In this lab we will enter a design using a structural or rtl description using the verilog hdl. you can create a verilog hdl input file (.v file) using the hdl editor available in the xilinx ise tools (or any text editor). What you'll learn familiar with verilog hdl syntax and semantics. use fundamental verilog constructs to create simple designs. creating synthesizable designs in verilog hdl to create simulation testbench on verilog and generating waveform's. Objective: to design all types the logic gates using verilog hdl programming and verify their simulation and synthesis reports. software and hardware: xilinx ise 9.2i and fpga spartan 3e. theory: a logic gate performs a logical operation on one or more logic inputs and produces a single logic output.

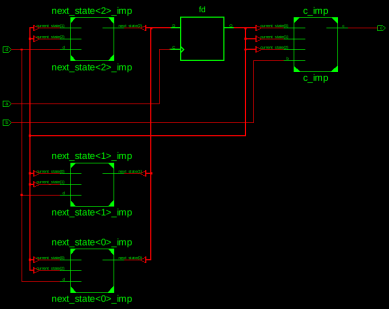

Digital Design And Synthesis Verilog Hdl Xilinx Ise By Jay Kim What you'll learn familiar with verilog hdl syntax and semantics. use fundamental verilog constructs to create simple designs. creating synthesizable designs in verilog hdl to create simulation testbench on verilog and generating waveform's. Objective: to design all types the logic gates using verilog hdl programming and verify their simulation and synthesis reports. software and hardware: xilinx ise 9.2i and fpga spartan 3e. theory: a logic gate performs a logical operation on one or more logic inputs and produces a single logic output. In order to write a verilog hdl description of any circuit you will need to write a module, which is the fundamental descriptive unit in verilog. a module is a set of text describing your circuit and is enclosed by the key words module and endmodule. Improved programming ability by mastering verilog hdl hardware description language and moore state machine; xilinx ise software allows for the design of various electronic circuits. Xilinx ise tutorial verilog, how to simulate verilog code in xilinx, xilinx ise 14.7 tutorial, xilinx vhdl code examples, how to simulate vhdl code in xilinx. Design and implementation of the following cmos digital analog circuits using cadence cad tools. the design shall include design, transistor level design, hierarchical design, verilog hdl vhdl design, logic synthesis, simulation and verification, scaling of cmos inverter for different technologies,.

Simulate Design Using Verilog Hdl In Modelsim And Chegg In order to write a verilog hdl description of any circuit you will need to write a module, which is the fundamental descriptive unit in verilog. a module is a set of text describing your circuit and is enclosed by the key words module and endmodule. Improved programming ability by mastering verilog hdl hardware description language and moore state machine; xilinx ise software allows for the design of various electronic circuits. Xilinx ise tutorial verilog, how to simulate verilog code in xilinx, xilinx ise 14.7 tutorial, xilinx vhdl code examples, how to simulate vhdl code in xilinx. Design and implementation of the following cmos digital analog circuits using cadence cad tools. the design shall include design, transistor level design, hierarchical design, verilog hdl vhdl design, logic synthesis, simulation and verification, scaling of cmos inverter for different technologies,.

Comments are closed.