Vlsi Lecture 7e Basic Timing Constraints

Synthesis Timing Constraints Waveform 2 Vlsi Tutorials Lecture 7 discusses sequential synchronous circuit design, including the overall approach, timing constraints and the design of sequential elements. section 7e presents the basic timing constraints. Watch?v=kag1dx3lnpg&list=plzu5hll 713yf0lkwjj9o3ttviuhpv me, 视频播放量 1、弹幕量 0、点赞数 0、投硬币枚数 0、收藏人数 0、转发人数 0, 视频作者 wz18207, 作者简介 zektbach bemni ひなビタ厨 喜欢物语 架空叙事故事 在读工学博士,相关视频:vlsi lecture 8b the.

Synthesis Timing Constraints 2 4 Vlsi Tutorials Before we learn about how to apply timing constraints to input, internal or output paths, we need to first understand the definition of a path. when a synthesis tool perform timing analysis, it break the design into timing paths. Transmission gate logic using cmos | circuit construction and working | simplified vlsi the backbench engineering community • 11k views • 2 years ago. Section 11b: additional issues in sign off timing. section 11d: sign off validation, including ir drop and em analysis, lec, and drc lvs erc. preparation of these recorded lectures was kindly supported by intel. tl. Bar ilan university 83 612: digital vlsi design in this course, i cover the basics of chip implementation, from designing the logic (rtl) to providing a layo.

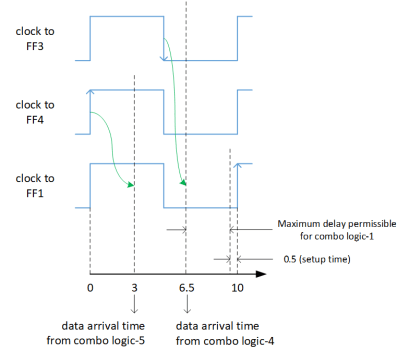

Synthesis Timing Constraints Waveform 1 Vlsi Tutorials Section 11b: additional issues in sign off timing. section 11d: sign off validation, including ir drop and em analysis, lec, and drc lvs erc. preparation of these recorded lectures was kindly supported by intel. tl. Bar ilan university 83 612: digital vlsi design in this course, i cover the basics of chip implementation, from designing the logic (rtl) to providing a layo. Bar ilan university 83 313: digital integrated circuits this lecture series teaches about designing digital circuits, starting with the technology, through t. Correct timing in synchronous logic generally means that every flip flop meets its basic timing requirements which include setup and hold timing (for synchronous inputs) and removal and recovery timing (for asynchronous inputs). Timing constraints: how do i connect my top level source signals to pins on my fpga?. In this course, i teach the fundamentals of digital circuit design with a focus on vlsi and process technologies, including methodologies, trade offs, and secondary effects in modern technologies.

Comments are closed.