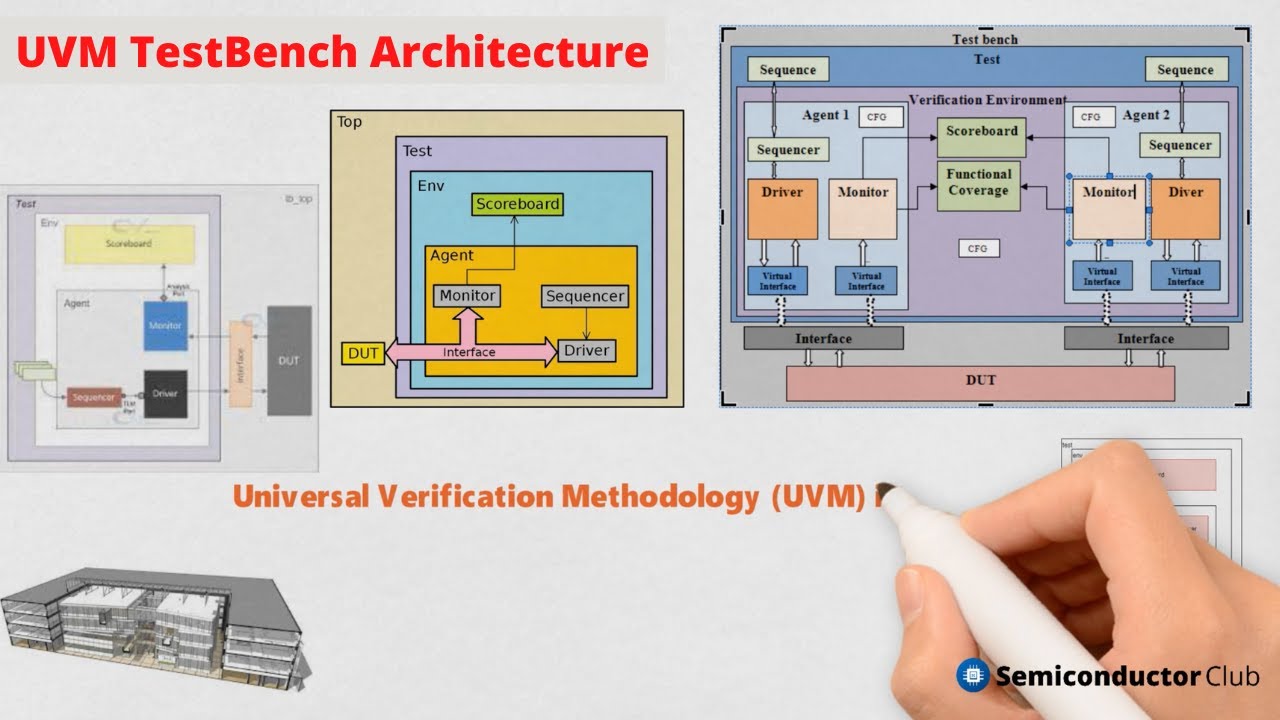

Uvm Base Classes Hierarchy Universal Verification Methodology Systemverilog Soc Verification

Uvm Universal Verification Methodology Springerlink 49 Off Uvm树状图 其中,各组件及验证平台的通讯方式包括config db及tlm, config db机制用于 uvm验证平台间(如test top向env中driver传递参数) 传递参数,tlm用于 验证平台内部(如monitor向scoreboard传递数据,隶属于同一验证平台) 的通讯。. Uvm学习笔记说明:这部分内容比较零散,且很多不好理解,所以这里只能选择性介绍一些内容。 使用interface代替driver部分功能 方法: 在interface中可以定义任务与函数,也可以使用always语句和initial语句,也可以实例化其他interface。可用其做一些低层次的转换, 如8b10b转换、 曼彻斯特编码等。….

Course Systemverilog Oop For Uvm Verification Session1 Classes Drich V2.3 uvm项目实战 很重要,建议重点学习; 项目不宜过多,应该以说明问题帮助理解掌握为目标。 v2.4 验证流程管理 对于新手来说,进去就是干活,项目的管理应该在实际项目中学习; 因此,获得进入一个不错企业平台的敲门砖比学这些“管理”既实在又重要得. `uvm object utils end component `uvm component utils begin `uvm component utils end filed机制的数据类型包括一下几种,是什么类型的数据,就注册什么样的数据类型。 field automation的第一个参数为要注册的数据,第二个参数为标志位(打开或关闭某个功能)。 11、sequence机制之sequence. Uvm各个component之间的通信机制归根结底就是当前的component handle通过获取对方的handle,直接调用对方的function task,给对方发送信息。. 建议顺序:绿白红。 绿皮书是基本的sv语法入门,为uvm学习打基础。 白皮书让你从0到1逐渐了解 uvm 架构的魅力。 红皮书是uvm 方法学 的深层次运用。.

System And Functional Verification Using Uvm Universal Verification Uvm各个component之间的通信机制归根结底就是当前的component handle通过获取对方的handle,直接调用对方的function task,给对方发送信息。. 建议顺序:绿白红。 绿皮书是基本的sv语法入门,为uvm学习打基础。 白皮书让你从0到1逐渐了解 uvm 架构的魅力。 红皮书是uvm 方法学 的深层次运用。. Uvm消息机制(uvm cookbook整理笔记5) initial the uvm messaging system uvm messaging uvm消息传递系统提供了从uvm testbench以一致格式打印消息的基本构件。 消息传递服务内置在所有uvm组件中,这是因为它们是从uvm report handler扩展的,uvm类继承关系如图所示。. 基于uvm方法学的异步fifo模块级验证平台。. 是什么? 1:new ()是 systemverilog 中的类构造函数。 2:type id::create是uvm中特有的方法。 两者都是为了创造对象 区别? 前者在创建对象时候需要指定内存,分配空间。 后者在创建对象时使用 factory机制,在uvm地图中注册,可以更好的配置,override,和控制其存在的时间。. 1. 引言 这篇文章主要应某位粉丝的要求写的,主要从应用角度讲解如何把模块级的寄存器模型复用到系统级,就不去细究uvm源码的实现原理了,所以就没有放在 [uvm源代码分析]的专栏里。 寄存器模型有个很基础的概念,就是寄存器模型本身是与接口协议无关的,它只跟spec定义的寄存器地址位宽.

Universal Verification Methodology Uvm Tessolve Uvm消息机制(uvm cookbook整理笔记5) initial the uvm messaging system uvm messaging uvm消息传递系统提供了从uvm testbench以一致格式打印消息的基本构件。 消息传递服务内置在所有uvm组件中,这是因为它们是从uvm report handler扩展的,uvm类继承关系如图所示。. 基于uvm方法学的异步fifo模块级验证平台。. 是什么? 1:new ()是 systemverilog 中的类构造函数。 2:type id::create是uvm中特有的方法。 两者都是为了创造对象 区别? 前者在创建对象时候需要指定内存,分配空间。 后者在创建对象时使用 factory机制,在uvm地图中注册,可以更好的配置,override,和控制其存在的时间。. 1. 引言 这篇文章主要应某位粉丝的要求写的,主要从应用角度讲解如何把模块级的寄存器模型复用到系统级,就不去细究uvm源码的实现原理了,所以就没有放在 [uvm源代码分析]的专栏里。 寄存器模型有个很基础的概念,就是寄存器模型本身是与接口协议无关的,它只跟spec定义的寄存器地址位宽.

Universal Verification Methodology Uvm Tessolve 是什么? 1:new ()是 systemverilog 中的类构造函数。 2:type id::create是uvm中特有的方法。 两者都是为了创造对象 区别? 前者在创建对象时候需要指定内存,分配空间。 后者在创建对象时使用 factory机制,在uvm地图中注册,可以更好的配置,override,和控制其存在的时间。. 1. 引言 这篇文章主要应某位粉丝的要求写的,主要从应用角度讲解如何把模块级的寄存器模型复用到系统级,就不去细究uvm源码的实现原理了,所以就没有放在 [uvm源代码分析]的专栏里。 寄存器模型有个很基础的概念,就是寄存器模型本身是与接口协议无关的,它只跟spec定义的寄存器地址位宽.

Universal Verification Methodology Uvm Tessolve

Comments are closed.