Transistors 6t Sram Simulation On Cadence Electrical Engineering

6t Sram Simulation Pdf Pdf Random Access Memory Mosfet I had recently studied about sram in computer architecture and learned that a sram cell is actually made up of mosfets. i was curious to learn more about the architecture of sram, for which i read some journal articles on 6t sram cell and decided to simulate it on cadence. This project focuses on the transistor level design and simulation of a 6 transistor (6t) static random access memory (sram) cell using cadence virtuoso. the 6t sram is a widely used memory element in digital systems due to its speed, low power consumption, and stability.

Design And Simulation Of 6t Sram Cell Architectures In 32nm Technology This paper presents the design and analysis of a low power 6 transistor (6t) static random access memory (sram) cell using 180nm cmos technology in the cadence virtuoso environment. Abstract—this project presents the design and implementation of a static random access memory (sram) system using the cadence virtuoso. sram is a key component in modern digital systems, particularly in cache memory, due to its high speed, low latency, and low static power consumption. In this video, i demonstrate the complete schematic design and simulation of a 6t sram (static random access memory) cell using [tool name – e.g., cadence virtuoso tanner eda]. more. This project focuses on the design and performance analysis of a 6 transistor (6t) sram cell using cadence virtuoso at two different technology nodes: 180nm and 90nm.

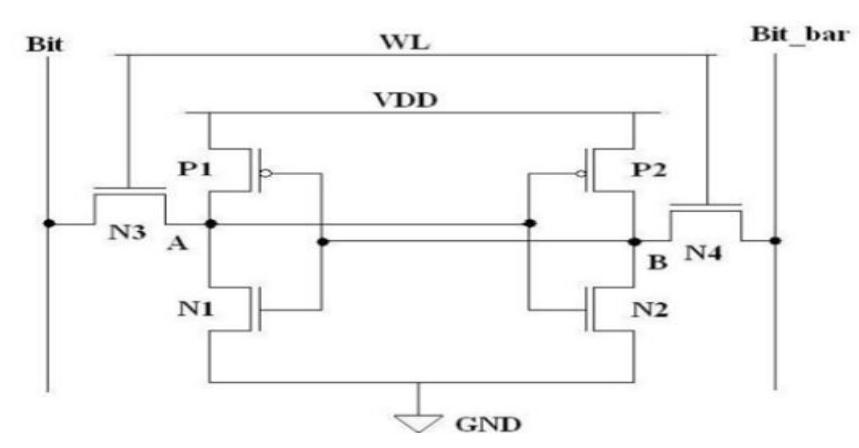

Transistors 6t Sram Simulation On Cadence Electrical Engineering In this video, i demonstrate the complete schematic design and simulation of a 6t sram (static random access memory) cell using [tool name – e.g., cadence virtuoso tanner eda]. more. This project focuses on the design and performance analysis of a 6 transistor (6t) sram cell using cadence virtuoso at two different technology nodes: 180nm and 90nm. 3 6t sram cell sizing os of various devices until the cell fails. create a new cell in your library called sram6t and generate a schematic similar to the one shown. A 6t sram cell layout and array design was proposed. 6t sram are the most widely used memory cells due to their compact size and eficiency. the w l ratio of the transistors in sram cell impact the stability. This research investigates the performance optimization of a 6t sram cell design in 90nm and 45nm technologies. focused on reducing both power consumption, acce. In this paper, the design and analysis of cmos based 6t sram cell at different technology nodes is demonstrated.

Transistors 6t Sram Simulation On Cadence Electrical Engineering 3 6t sram cell sizing os of various devices until the cell fails. create a new cell in your library called sram6t and generate a schematic similar to the one shown. A 6t sram cell layout and array design was proposed. 6t sram are the most widely used memory cells due to their compact size and eficiency. the w l ratio of the transistors in sram cell impact the stability. This research investigates the performance optimization of a 6t sram cell design in 90nm and 45nm technologies. focused on reducing both power consumption, acce. In this paper, the design and analysis of cmos based 6t sram cell at different technology nodes is demonstrated.

Transistors 6t Sram Simulation On Cadence Electrical Engineering This research investigates the performance optimization of a 6t sram cell design in 90nm and 45nm technologies. focused on reducing both power consumption, acce. In this paper, the design and analysis of cmos based 6t sram cell at different technology nodes is demonstrated.

Circuit Diagram Of 6t Sram Cell Using Cmos Transistors The

Comments are closed.