The On Chip Learning Algorithm

On Chip Training Npu Algorithm Architecture And Soc Design The study demonstrates a real time neural decoding task with an analog adaptive circuit. the on chip learning algorithm is developed to adapt the parameters of the analog adaptive circuit. In this work, we demonstrated a memristor based neuro inspired computing chip that enabled fully on chip learning, for which a memristor featured sign and threshold based learning (stellar) architecture was proposed.

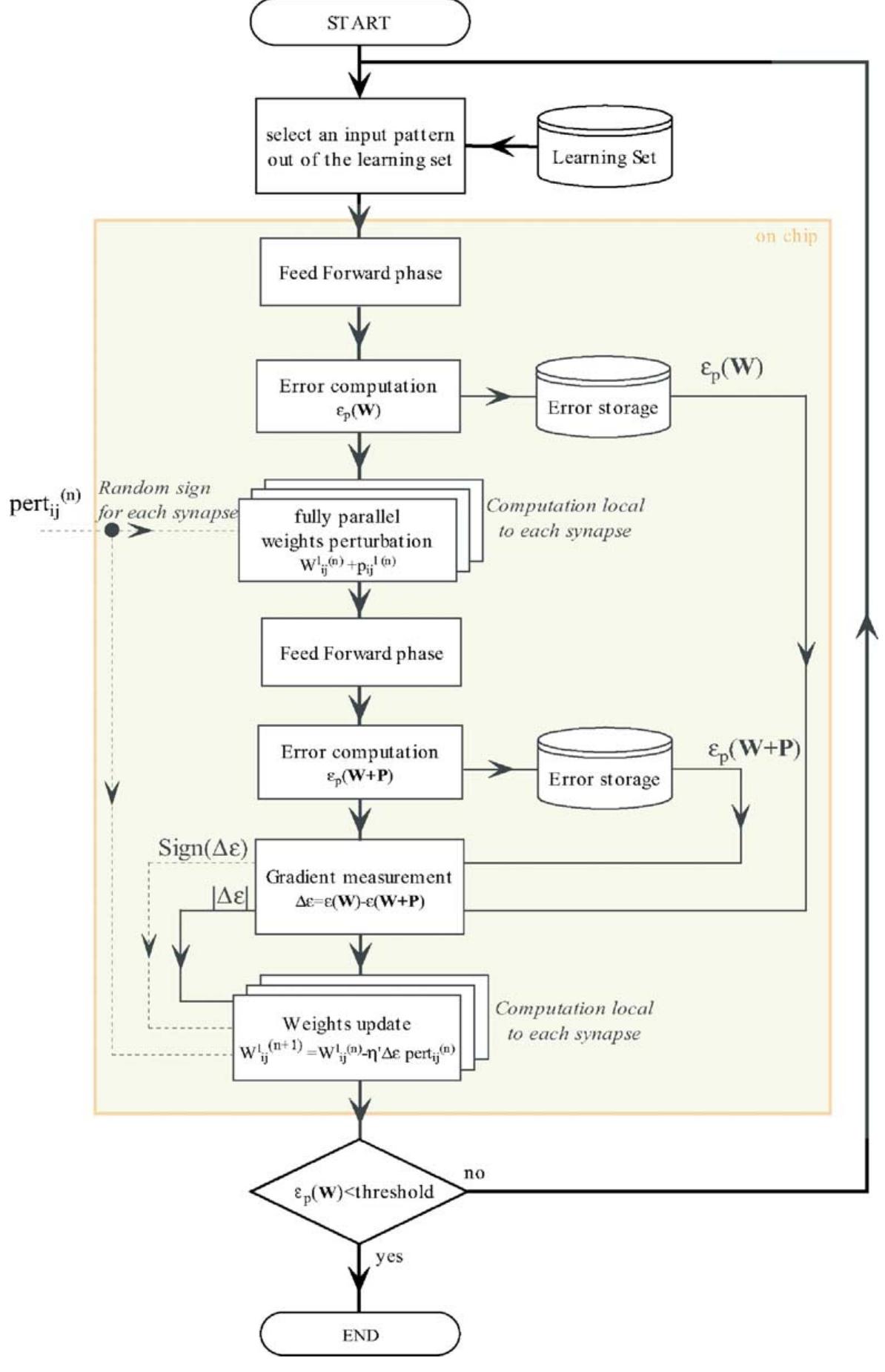

The On Chip Learning Algorithm Here, we propose an on chip learning algorithm, named sign backpropagation (sbp), for rram based multilayer perceptron (mlp) with binary interfaces (0, 1) in forward process and 2 bit (± 1, 0) in backward process. This study investigates machine learning (ml) techniques for optimizing network on chip (noc) application mapping, focusing on supervised learning, unsupervised learning, reinforcement learning, and neural networks. This work presents such an algorithm, illustrated in the flowchart in fig. 6, for on chip training of memristors and adjusting synaptic weights. the training algorithm begins by examining the weights extracted from the trained neural network model to train the 30 synaptic memristors. They propose a combination of techniques for deployment of next generation of on chip machine learning including hardware aware dnns that could allow for this stage to be on chip as opposed to offline.

Chip Algorithm Stock Illustrations 2 956 Chip Algorithm Stock This work presents such an algorithm, illustrated in the flowchart in fig. 6, for on chip training of memristors and adjusting synaptic weights. the training algorithm begins by examining the weights extracted from the trained neural network model to train the 30 synaptic memristors. They propose a combination of techniques for deployment of next generation of on chip machine learning including hardware aware dnns that could allow for this stage to be on chip as opposed to offline. Running a spiking convolutional form of the locally competitive algorithm, loihi can solve lasso optimization problems with over three orders of magnitude superior energy delay product compared to conventional solvers running on a cpu iso process voltage area. Here, we study the compatibility of hnn learning rules to onn on chip learning for pattern recognition and implement the compatible learning rules in our digital onn on chip learning architecture. To address this bottleneck, this study introduces a novel mnn paradigm that facilitates fully on chip learning. critically, this neuromorphic system adopts an operational mechanism derived from biological principles—contrastive hebbian learning. Here, we propose an on chip learning algorithm, named sign backpropagation (sbp), for rram based multilayer perceptron (mlp) with binary interfaces (0, 1) in forward process and 2 bit (±1,.

Chip Algorithm Stock Illustrations 2 956 Chip Algorithm Stock Running a spiking convolutional form of the locally competitive algorithm, loihi can solve lasso optimization problems with over three orders of magnitude superior energy delay product compared to conventional solvers running on a cpu iso process voltage area. Here, we study the compatibility of hnn learning rules to onn on chip learning for pattern recognition and implement the compatible learning rules in our digital onn on chip learning architecture. To address this bottleneck, this study introduces a novel mnn paradigm that facilitates fully on chip learning. critically, this neuromorphic system adopts an operational mechanism derived from biological principles—contrastive hebbian learning. Here, we propose an on chip learning algorithm, named sign backpropagation (sbp), for rram based multilayer perceptron (mlp) with binary interfaces (0, 1) in forward process and 2 bit (±1,.

Chip Algorithm Stock Illustrations 2 956 Chip Algorithm Stock To address this bottleneck, this study introduces a novel mnn paradigm that facilitates fully on chip learning. critically, this neuromorphic system adopts an operational mechanism derived from biological principles—contrastive hebbian learning. Here, we propose an on chip learning algorithm, named sign backpropagation (sbp), for rram based multilayer perceptron (mlp) with binary interfaces (0, 1) in forward process and 2 bit (±1,.

Comments are closed.