Systemverilog Tutorial In 5 Minutes 17a Concurrent Assertions

Systemverilog Concurrent Assertions Enjoy the videos and music you love, upload original content, and share it all with friends, family, and the world on . A tutorial on systemverilog assertions, including immediate and concurrent assertions, assume, assert and cover properties, how to use systemverilog bind, and a rich collection of examples you can use as reference.

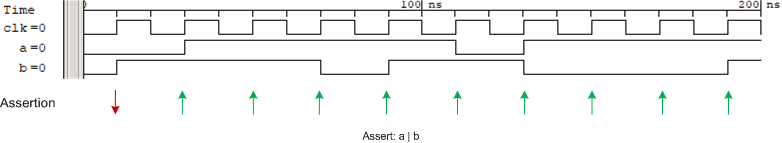

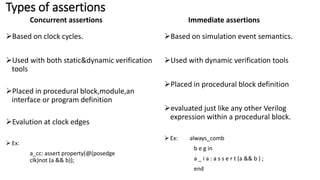

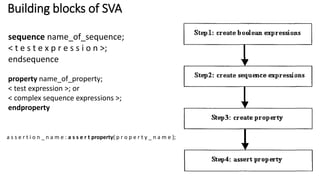

Systemverilog Assertions Tutorial Pdf Areas Of Computer Science Assertions are powerful statements that automatically check your design's behavior during simulation. they catch bugs immediately when they happen, not hours later when you're debugging waveforms. this is your complete guide to mastering sva. Concurrent assertions describe behavior that spans over time. concurrent assertion is evaluated only at the occurrence of a clock tick. the values of variables used in the evaluation are the sampled values. In systemverilog there are two kinds of assertions: immediate (assert) and concurrent (assert property). coverage statements (cover property) are concurrent and have the same syntax as concurrent assertions, as do assume property statements. An assertion is a check embedded in design or bound to a design unit during the simulation. warnings or errors are generated on the failure of a specific condition or sequence of events.

System Verilog Assertions Pptx In systemverilog there are two kinds of assertions: immediate (assert) and concurrent (assert property). coverage statements (cover property) are concurrent and have the same syntax as concurrent assertions, as do assume property statements. An assertion is a check embedded in design or bound to a design unit during the simulation. warnings or errors are generated on the failure of a specific condition or sequence of events. Concurrent assertions describe behavior that spans over simulation time and are evaluated only at the occurence of a clock tick. systemverilog concurrent assertion statements can be specified in a module, interface or program block running concurrently with other statements. There are two types of assertions: immediate and concurrent. i will omit immediate here because they are simple and straightforward for anyone who wrote an assertions in any language. If for every successful attempt (req==1) gnt==1 4 to 32 cycles later, then the assertion passes, else it fails. every attempt is separate and independent from other attempts, and each attempt has a life of its own. Assertions are statements used to validate the behavior of a design during simulation. they help catch protocol violations, timing errors, and unexpected signal interactions early in the verification cycle.

System Verilog Assertions Pptx Concurrent assertions describe behavior that spans over simulation time and are evaluated only at the occurence of a clock tick. systemverilog concurrent assertion statements can be specified in a module, interface or program block running concurrently with other statements. There are two types of assertions: immediate and concurrent. i will omit immediate here because they are simple and straightforward for anyone who wrote an assertions in any language. If for every successful attempt (req==1) gnt==1 4 to 32 cycles later, then the assertion passes, else it fails. every attempt is separate and independent from other attempts, and each attempt has a life of its own. Assertions are statements used to validate the behavior of a design during simulation. they help catch protocol violations, timing errors, and unexpected signal interactions early in the verification cycle.

Comments are closed.