Systemverilog Assertions Learning Curve

Systemverilog Assertions Basics Pdf Mathematical Logic Computer Foundation to start your systemverilog assertion learning journey [1] what are assertions [2] sva breakup base, accessories and packaging [4] learning curve for more detailed courses. A tutorial on systemverilog assertions, including immediate and concurrent assertions, assume, assert and cover properties, how to use systemverilog bind, and a rich collection of examples you can use as reference.

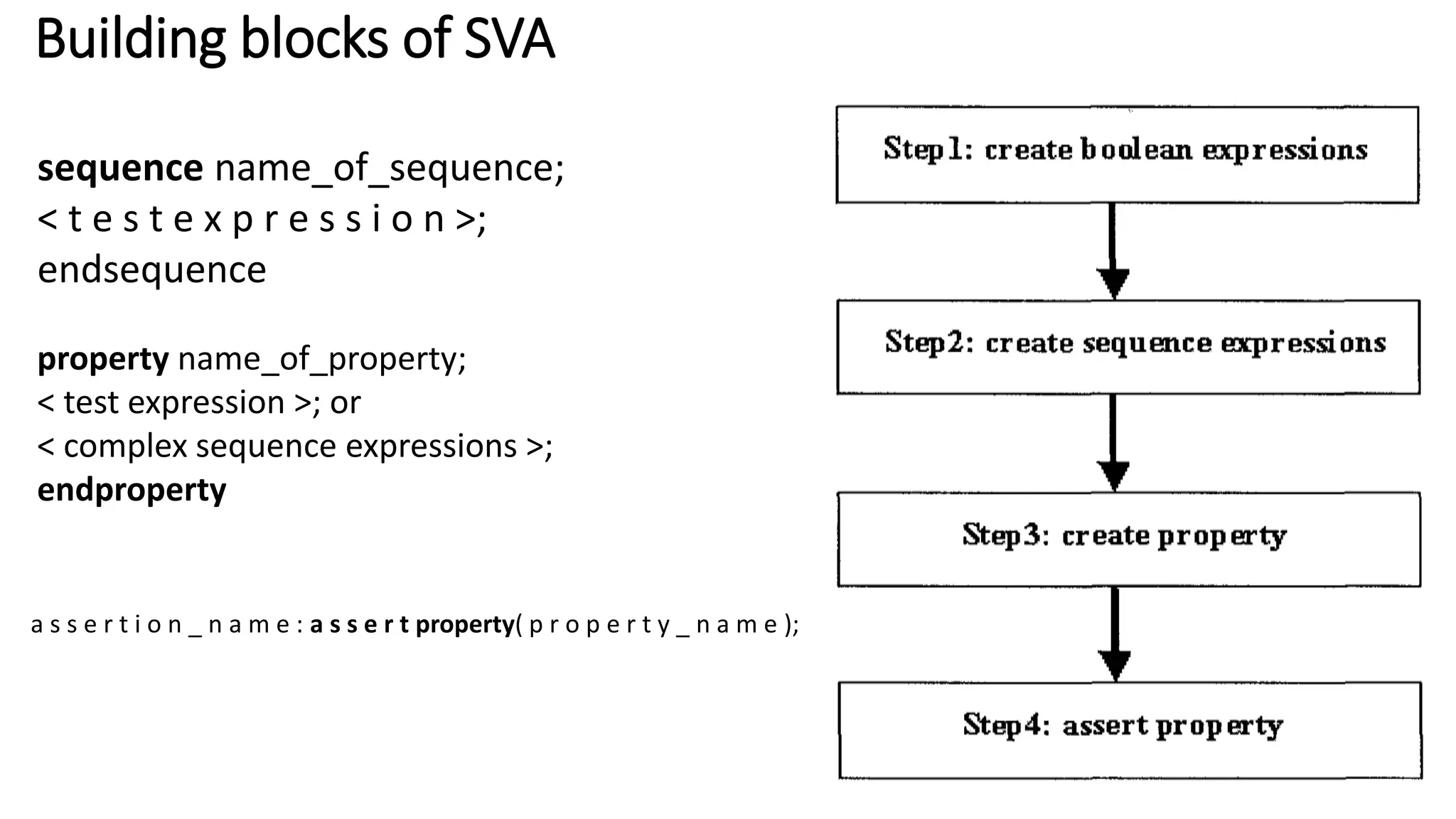

Systemverilog Assertions Interview Questions In systemverilog there are two kinds of assertions: immediate (assert) and concurrent (assert property). coverage statements (cover property) are concurrent and have the same syntax as concurrent assertions, as do assume property statements. Assertions are powerful statements that automatically check your design's behavior during simulation. they catch bugs immediately when they happen, not hours later when you're debugging waveforms. this is your complete guide to mastering sva. Systemverilog assertions (sva) are a powerful way to specify design behavior and check it during simulation or formal verification. this guide will explain sva in detail with examples to help you understand how to write effective assertions. An assertion is nothing but a more concise representation of a functional checker. the functionality represented by an assertion can also be written as a systemverilog task or checker that involves more line of code.

System Verilog Assertions Pptx Systemverilog assertions (sva) are a powerful way to specify design behavior and check it during simulation or formal verification. this guide will explain sva in detail with examples to help you understand how to write effective assertions. An assertion is nothing but a more concise representation of a functional checker. the functionality represented by an assertion can also be written as a systemverilog task or checker that involves more line of code. This course gives you an in depth introduction to systemverilog assertions (sva), together with guidelines and methodologies to help you create, manage, and debug effective assertions for complex design properties. An assertion is a check embedded in design or bound to a design unit during the simulation. warnings or errors are generated on the failure of a specific condition or sequence of events. Whether you’re a first time engineer or an experienced verification professional, this course will guide you from the basics of systemverilog assertions (sva) to becoming an expert in assertion based verification (abv). This page contains systemverilog tutorial, systemverilog syntax, systemverilog quick reference, dpi, systemverilog assertions, writing testbenches in systemverilog, lot of systemverilog examples and systemverilog in one day tutorial.

Comments are closed.