Systemverilog Assertion Systemverilog Verification Academy

Fifo Module Assertion Systemverilog Verification Academy Explore how advanced technologies and methodologies—spanning functional verification, safety, security, and more—are applied to solve real world design problems. this curated content brings together best practices, expert perspectives, and proven tools to accelerate verification success. Learn how to use systemverilog’s new verification blocks to improve the organization and effectiveness of your testbenches. understand how the systemverilog event scheduler divides time slots into distinct regions, providing better control over simulation actions.

Reset Assertion Systemverilog Verification Academy Systemverilog assertions (sva) is essentially a language construct which provides a powerful alternate way to write constraints, checkers and cover points for your design. it lets you express rules (i.e., english sentences) in the design specification in a systemverilog format which tools can understand. During my years of contributions to the verification academy systemverilog forum, i have seen many trends in real users’ difficulties in the application of assertions, and misunderstandings of how sva works. Assertion coverage gives us an insight into which parts of the design's intended behavior have been tested and which have not. it helps identify areas of the design that need more testing and can highlight scenarios that have been missed in the test plan. This training details how the systemverilog assertion (sva) syntax works and how assertions can be used for design and verification. special macro techniques are shown to reduce assertion coding effort by up to 80%.

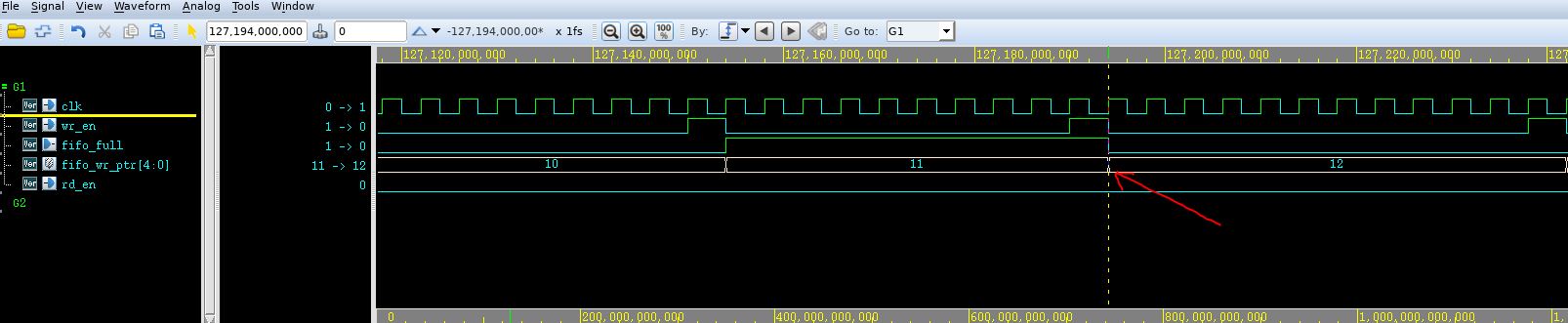

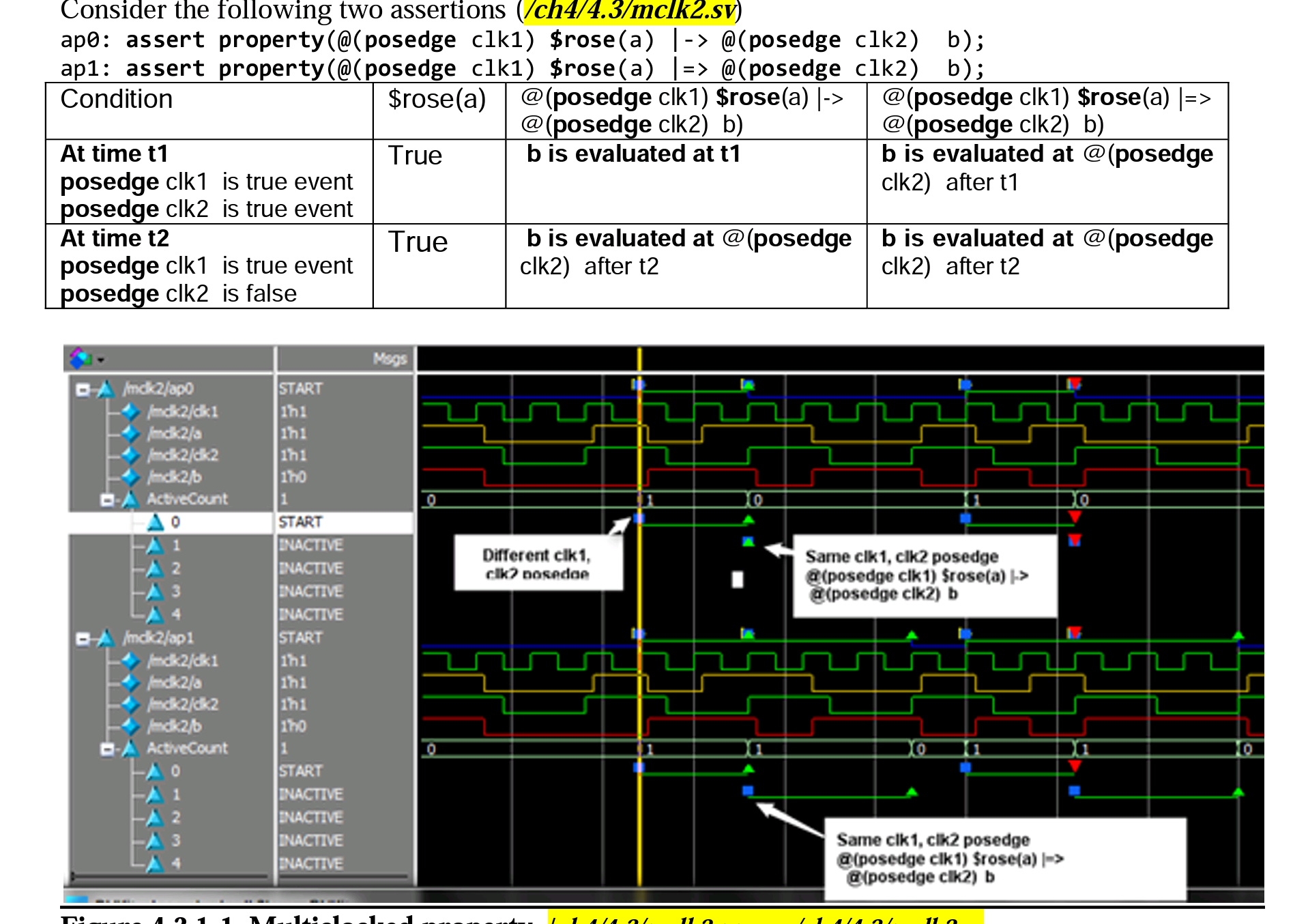

Waveform For This Assertion Systemverilog Verification Academy Assertion coverage gives us an insight into which parts of the design's intended behavior have been tested and which have not. it helps identify areas of the design that need more testing and can highlight scenarios that have been missed in the test plan. This training details how the systemverilog assertion (sva) syntax works and how assertions can be used for design and verification. special macro techniques are shown to reduce assertion coding effort by up to 80%. This course provides a comprehensive guide to creating and applying assertions in hardware design and verification. you'll learn how to harness assertions to monitor design properties dynamically through simulations and verify them exhaustively with static verification techniques. This 2 day course is intended for design and verification engineers who will learn how to write systemverilog assertions to check their designs. there are many hands on labs to reinforce lecture and discussion topics under the guidance of our industry expert instructors. I want to use an assertion to check the following scenario: signal a asserts for one cycle, then signal b asserts for one cycle and signal c asserts for one cycle (the problem here is: the order of b and c is arbitrary, so we don’t know when b and c will be asserted and who will be asserted first), then signal d should asserts right after the. Assertions can be checked dynamically by simulation, or statically by formal verification eda tool that proves whether the design meets its specification requirement or not. these tools require specifications about the design’s behavior. read the complete blog here systemverilog assertions. what are systemverilog assertions?.

Comments are closed.