Solved There Is A 6t Sram Static Random Access Memory Chegg

Design A Static Random Access Memory Sram Memory Chegg Unlock this question and get full access to detailed step by step answers. design a test circuit let cadence virtuoso and cosmos scope can plot the sram's reading 1,0 and writing 1,0 operation like the figure below. here’s the best way to solve it. Unleash the power of custom ic design with my 6t sram cell implementation. dive into the world of cutting edge ic design with my comprehensive project on a 6 transistor static random access memory (6t sram) cell.

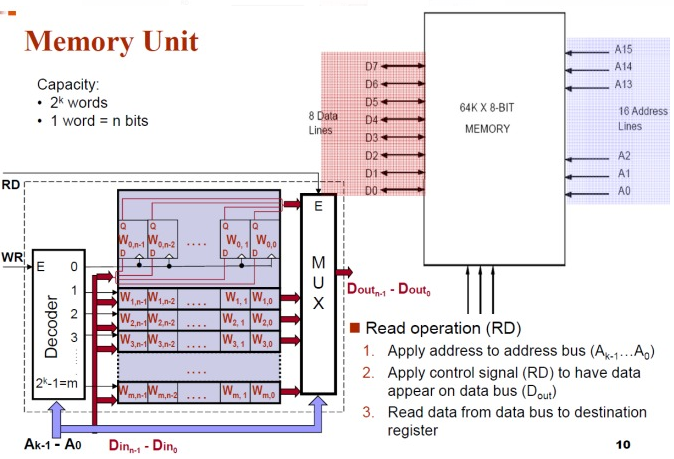

Sram Static Random Access Memory Stock Illustration 2466909905 Static random access memory, sometimes known as sram, is a type of semiconductor memory frequently employed in electronic, microprocessor, and general computing applications. The document describes the design and simulation of a simple 6 transistor static random access memory (sram) cell. it first reviews the basics of sram operation for read and write operations. Abstract—this project presents the design and implementation of a static random access memory (sram) system using the cadence virtuoso. sram is a key component in modern digital systems, particularly in cache memory, due to its high speed, low latency, and low static power consumption. Static random access memory (sram) can retain its stored information as long as power is supplied. this is in contrast to dynamic ram (dram) where periodic refreshes are necessary or non volatile memory where no power needs to be supplied for data retention, as for example flash memory.

Sram Static Random Access Memory How It Works Application Advantages Abstract—this project presents the design and implementation of a static random access memory (sram) system using the cadence virtuoso. sram is a key component in modern digital systems, particularly in cache memory, due to its high speed, low latency, and low static power consumption. Static random access memory (sram) can retain its stored information as long as power is supplied. this is in contrast to dynamic ram (dram) where periodic refreshes are necessary or non volatile memory where no power needs to be supplied for data retention, as for example flash memory. The fundamental building block of static random access memory (sram) is the 6 transistor (6t) sram cell, consisting of two cross coupled inverters and two access transistors. The document describes the design and simulation of a 6 transistor static random access memory (sram) cell. it first reviews the basics of sram operation, including how the 6t sram performs read and write operations. 1) 6t sram is a type of semiconductor memory that uses bistable latching circuitry to store each bit in a static manner without requiring periodic refreshing. 2) the circuit diagram shows a 6t sram cell consisting of two cross coupled inverters made of four transistors and two access transistors.

Github Pandey 99 Static Random Access Memory Sram Analysis The fundamental building block of static random access memory (sram) is the 6 transistor (6t) sram cell, consisting of two cross coupled inverters and two access transistors. The document describes the design and simulation of a 6 transistor static random access memory (sram) cell. it first reviews the basics of sram operation, including how the 6t sram performs read and write operations. 1) 6t sram is a type of semiconductor memory that uses bistable latching circuitry to store each bit in a static manner without requiring periodic refreshing. 2) the circuit diagram shows a 6t sram cell consisting of two cross coupled inverters made of four transistors and two access transistors.

Structure Of A Typical Static Random Access Memory Sram Memory 1) 6t sram is a type of semiconductor memory that uses bistable latching circuitry to store each bit in a static manner without requiring periodic refreshing. 2) the circuit diagram shows a 6t sram cell consisting of two cross coupled inverters made of four transistors and two access transistors.

Comments are closed.