Solved Problem Set 11 A Construct A 4 Bit Odd Parity Chegg

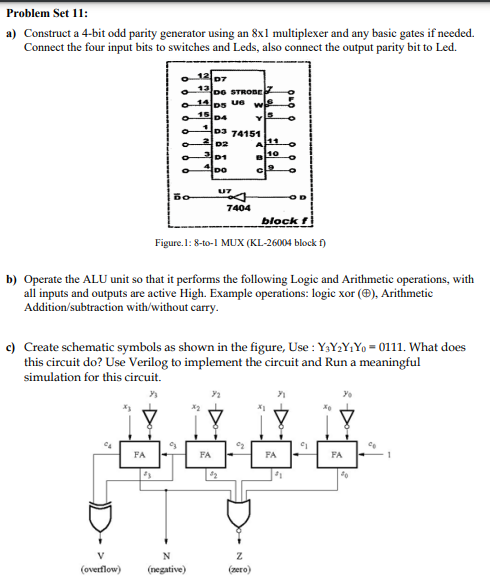

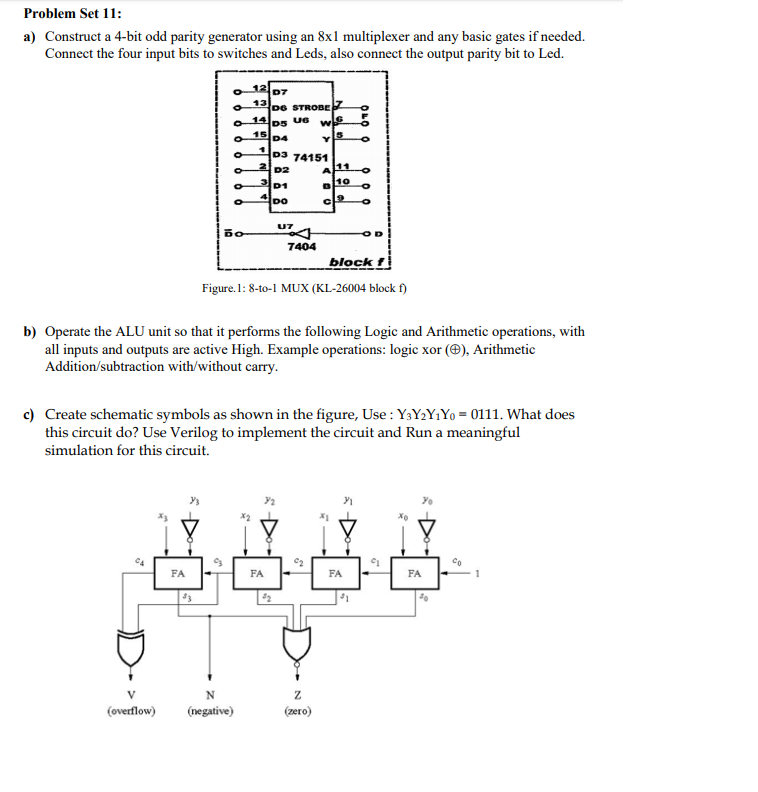

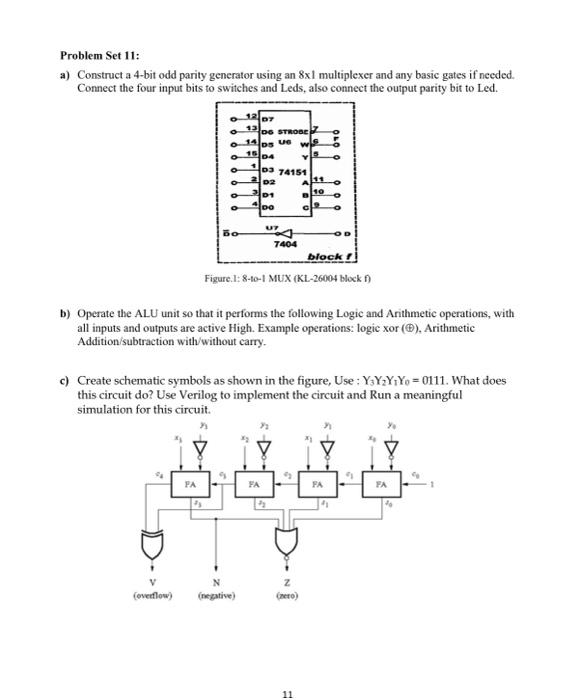

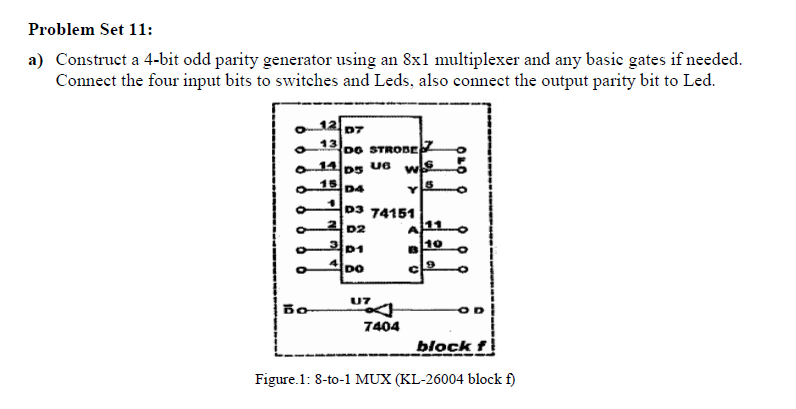

Solved Problem Set 11 A Construct A 4 Bit Odd Parity Chegg Problem set 11: a) construct a 4 bit odd parity generator using an 8x1 multiplexer and any basic gates if needed. connect the four input bits to switches and leds, also connect the output parity bit to led. Problem set 11: a) construct a 4 bit odd parity generator using an 8x1 multiplexer and any basic gates if needed.

Solved Problem Set 11 A Construct A 4 Bit Odd Parity Chegg Our expert help has broken down your problem into an easy to learn solution you can count on. question: problem set 11: a) construct a 4 bit odd parity generator using an 8xl multiplexer and any basic gates if needed. Construct an odd parity generator and the corresponding parity checker circuit by considering a 4 bit (a,b,c, and d) message to be transmitted along with an even parity bit ( p). Construct a 4 bit odd parity checker circuit with necessary logic gates. show your work. 437 views combinational parity bit 4 bit author: saranga k. mahanta project access type: public description: 4 bit odd parity bit generator using xor and xnor created: jul 03, 2020 updated: jun 30, 2023.

Solved Problem Set 11 A Construct A 4 Bit Odd Parity Chegg Construct a 4 bit odd parity checker circuit with necessary logic gates. show your work. 437 views combinational parity bit 4 bit author: saranga k. mahanta project access type: public description: 4 bit odd parity bit generator using xor and xnor created: jul 03, 2020 updated: jun 30, 2023. This document describes a micro project to build a 4 bit parity generator and checker circuit using reversible logic gates. a team of 5 students designed the circuits using ex or gates in a cascading structure to generate the parity bit. Step 1 2a) to design a 4 bit odd parity generator, we need to ensure that the output bit (p) is set to 1 if the number of 1s in the 4 bit input (a) is even, and set to 0 if the number of 1s is odd. The odd parity output for a 4 bit parity generator can be computed as described, and it can be efficiently implemented using a 4:1 multiplexer based on the specified configurations. Its primary function is to calculate and add the parity bit to the data stream based on the chosen parity scheme (even or odd). the circuit takes the original data stream (e.g., a byte) as input.

Solved Problem Set 11 A Construct A 4 Bit Odd Parity Chegg This document describes a micro project to build a 4 bit parity generator and checker circuit using reversible logic gates. a team of 5 students designed the circuits using ex or gates in a cascading structure to generate the parity bit. Step 1 2a) to design a 4 bit odd parity generator, we need to ensure that the output bit (p) is set to 1 if the number of 1s in the 4 bit input (a) is even, and set to 0 if the number of 1s is odd. The odd parity output for a 4 bit parity generator can be computed as described, and it can be efficiently implemented using a 4:1 multiplexer based on the specified configurations. Its primary function is to calculate and add the parity bit to the data stream based on the chosen parity scheme (even or odd). the circuit takes the original data stream (e.g., a byte) as input.

Solved Problem Set 11 A Construct A 4 Bit Odd Parity Chegg The odd parity output for a 4 bit parity generator can be computed as described, and it can be efficiently implemented using a 4:1 multiplexer based on the specified configurations. Its primary function is to calculate and add the parity bit to the data stream based on the chosen parity scheme (even or odd). the circuit takes the original data stream (e.g., a byte) as input.

Comments are closed.