Solved Problem 2 Data I Hazards Chapter 4 This Exercise Chegg

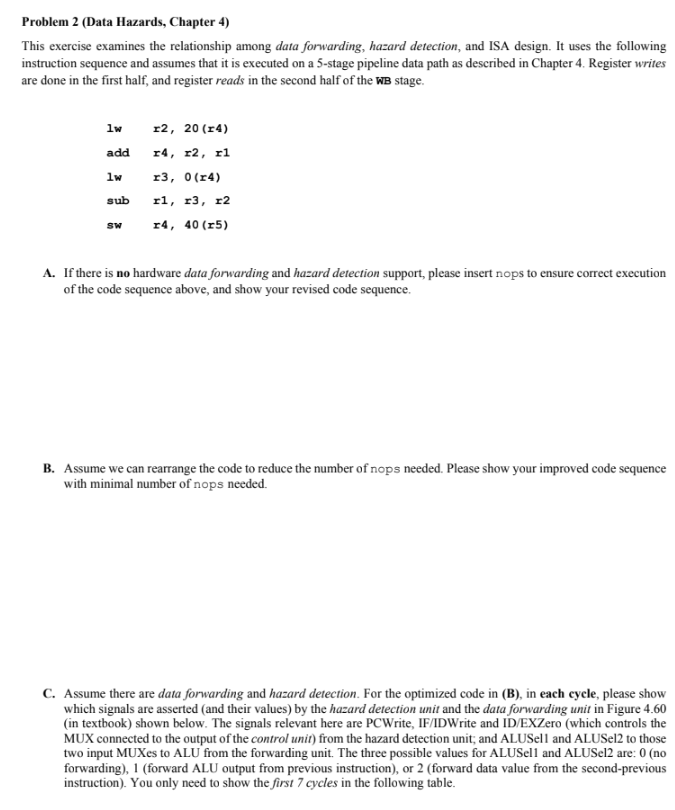

Solved Problem 2 Data ï Hazards Chapter 4 This Exercise Chegg Problem 2 (data hazards, chapter 4)this exercise examines the relationship among data forwarding, hazard detection, and isa design. it uses the following instruction sequence and assumes that it is executed on a 5 stage pipeline data path as described in chapter 4. This exercise examines the relationship among data forwarding, hazard detection, and isa design.

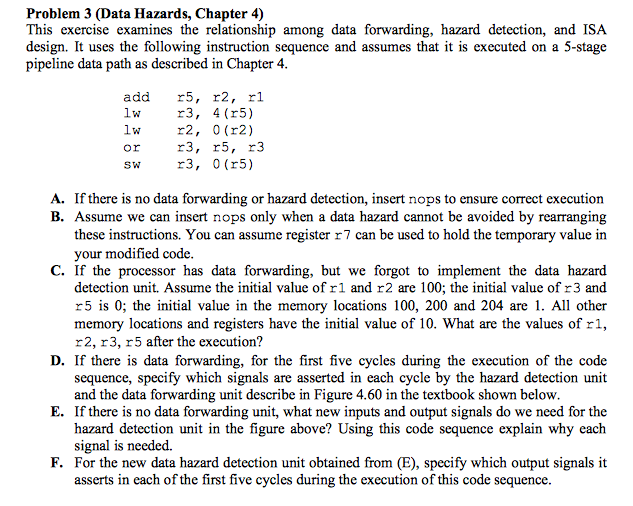

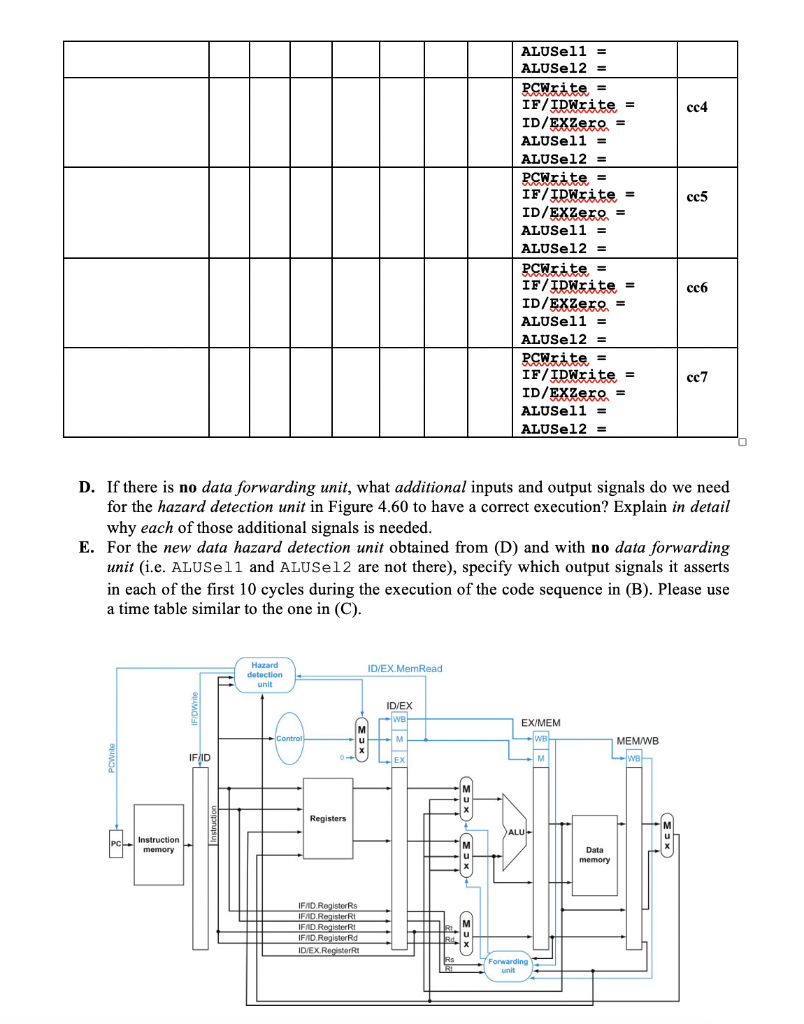

Problem 3 Data Hazards Chapter 4 This Exercise Chegg Our expert help has broken down your problem into an easy to learn solution you can count on. question: problem 2 (data hazards, chapter 4)this exercise examines the relationship among data forwarding, hazard detection, and isa design. register writes are done in the first half, and register can you help me with this problem? problem 2 (data hazards, chapter 4) this exercise examines the relationship among data forwarding, hazard detection, and isa design. Problem 2 (data hazards, chapter 4) this exercise examines the relationship among data forwarding, hazard detection, and isa design. it uses the following instruction sequence and assumes that it is executed on a 5 stage pipeline data path as described in chapter 4. The document provides a step by step solution to a problem related to a new hazard detection unit in a five stage pipelined datapath. it specifies the output signals for each of the first five cycles during the execution of a given sequence of instructions.

Problem 3 Data Hazards Chapter 4 This Exercise Chegg Problem 2 (data hazards, chapter 4) this exercise examines the relationship among data forwarding, hazard detection, and isa design. it uses the following instruction sequence and assumes that it is executed on a 5 stage pipeline data path as described in chapter 4. The document provides a step by step solution to a problem related to a new hazard detection unit in a five stage pipelined datapath. it specifies the output signals for each of the first five cycles during the execution of a given sequence of instructions. The document outlines a problem related to pipeline processing in computer organization, specifically focusing on handling data hazards with nop instructions. it discusses the calculations for pipeline performance with and without forwarding, emphasizing the need for fewer nops to improve efficiency. Stalling means it makes the instructions to wait to get rid of hazards, and forwarding helps to solve data hazards by fetching the missed information from the internal buffer itself rather than getting from the register memory. Computer organization and design: the hardware software interface david a. patterson,… 4th edition chapter 4, problem 2 instant answer step 1. To guarantee forward progress, this hazard must always be resolved in favor of the instruction that accesses data. what is the total execution time of this instruction sequence in the 5 stage pipeline that only has one memory?.

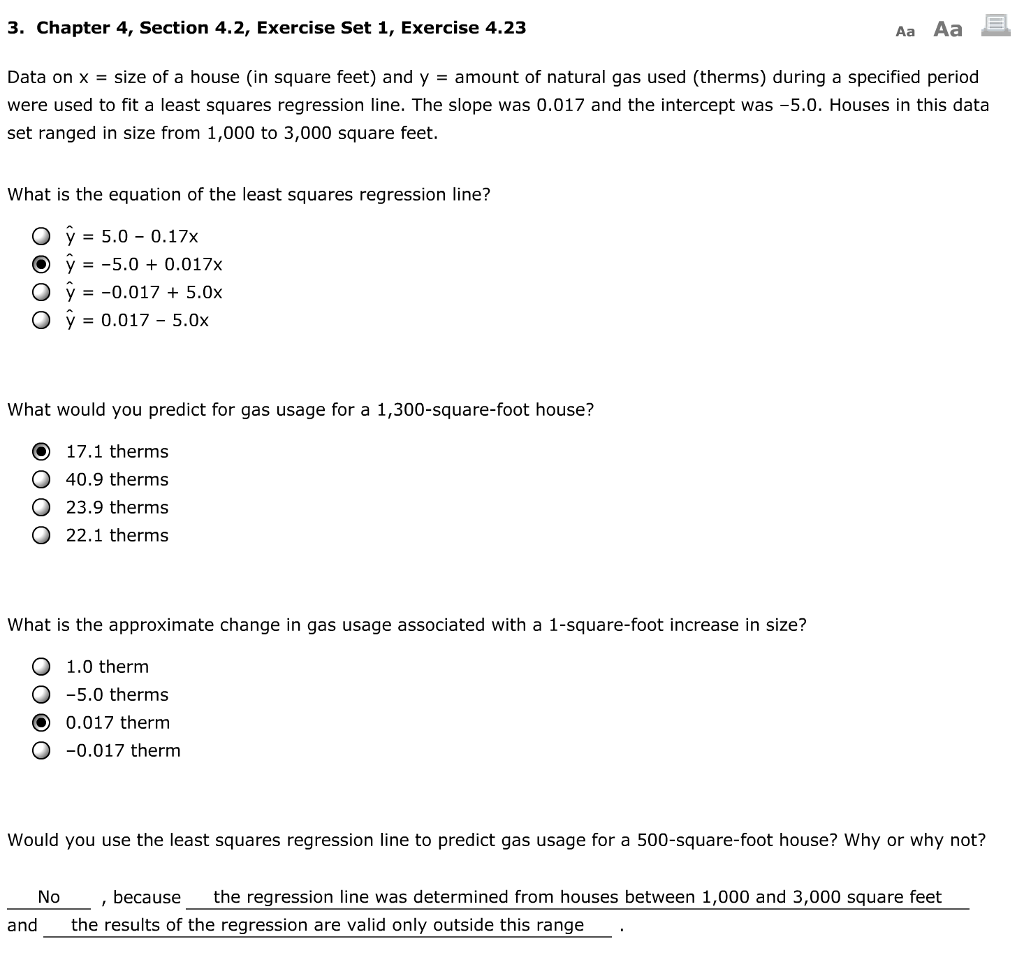

Solved 3 Chapter 4 Section 4 2 Exercise Set 1 Exercise Chegg The document outlines a problem related to pipeline processing in computer organization, specifically focusing on handling data hazards with nop instructions. it discusses the calculations for pipeline performance with and without forwarding, emphasizing the need for fewer nops to improve efficiency. Stalling means it makes the instructions to wait to get rid of hazards, and forwarding helps to solve data hazards by fetching the missed information from the internal buffer itself rather than getting from the register memory. Computer organization and design: the hardware software interface david a. patterson,… 4th edition chapter 4, problem 2 instant answer step 1. To guarantee forward progress, this hazard must always be resolved in favor of the instruction that accesses data. what is the total execution time of this instruction sequence in the 5 stage pipeline that only has one memory?.

Comments are closed.