Soc Verification Flow And Methodologies

Soc Verification Flow And Methodologies By Sivakumar Pr Pdf System In this article, let me walk you through various verification methodologies we use for verifying ips, sub systems, and socs and explain why we need new methodologies standards like pss. The document discusses verification methodologies for ips, subsystems, and socs. it explains that designing complex chips requires extensive verification at every level using various methodologies.

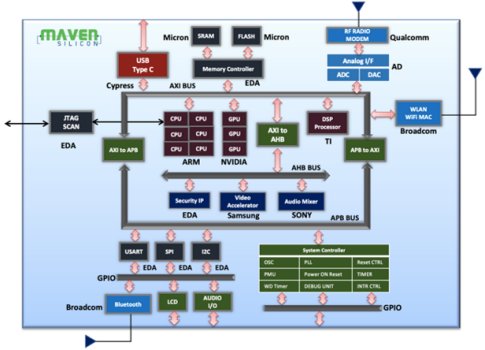

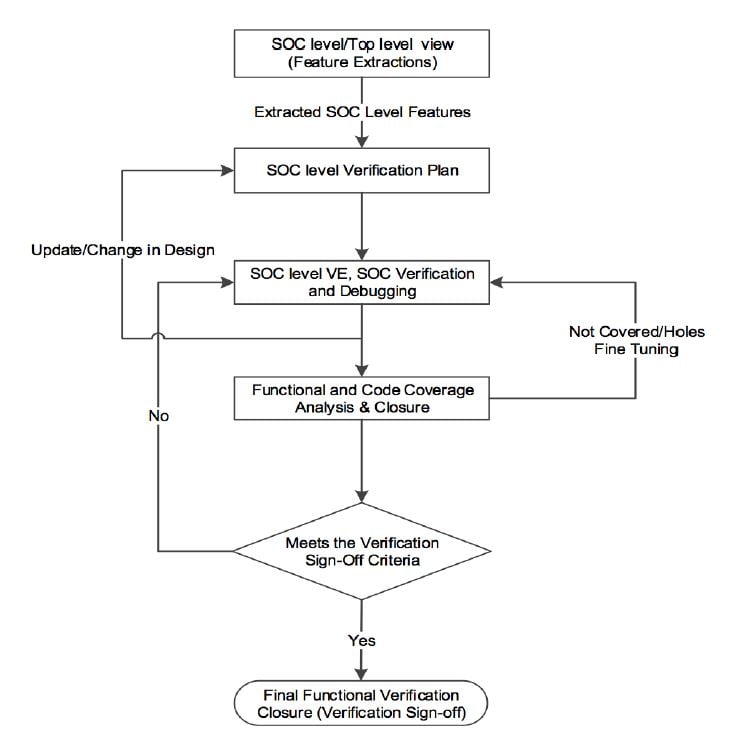

Soc Verification Flow And Methodologies The technologies of static verification such as lint checking and static timing verification verification don’t require test vectors or testbench for performing verification. Discover the ultimate guide to soc verification methodologies, covering the latest techniques and best practices for ensuring system on chip design reliability and performance. In this article, let us walk you through various verification methodologies we use for verifying ips, sub systems, and socs and explain why we need new methodologies standards like pss. Verification of an soc design is carried out at different stages with a different approach as per design specifications. with interconnect as a common ground for all the rest of the design to interact, there are many functionalities to be verified and connectivity checks to be conducted.

Soc Verification Flow Semiconductor Club In this article, let us walk you through various verification methodologies we use for verifying ips, sub systems, and socs and explain why we need new methodologies standards like pss. Verification of an soc design is carried out at different stages with a different approach as per design specifications. with interconnect as a common ground for all the rest of the design to interact, there are many functionalities to be verified and connectivity checks to be conducted. With technological advancements and rising customer expectations, socs have become an integral component of highly complex electronic and computing devices. therefore, verifying these complex soc designs with efficient methodologies (reducing time and cost) becomes important before tapeout. Modern soc design flow. the soc design flow is illustrated in fig. 2. it outlines the steps in designing a modern soc at a very high level. due to the pressures of shrinking time to market and rising production costs, it has become nearly impossible for a single entity to manage the entire process . This paper gives an idea of how a soc is going to verify covering all its functionality using verification methodology‟s parameter such as functional coverage and code coverage. using verification techniques and verification approach we can verify system level soc. We look at typical soc designs and the traditional verification techniques applied to them, commenting on their benefits and inherent limitations. as part of that, we mention the components of an soc and some effect they have on the design of the testbench.

Comments are closed.